sony_cdx-gt707dx.pdf

-

Upload

marcioulguim -

Category

Documents

-

view

22 -

download

3

Transcript of sony_cdx-gt707dx.pdf

MANUAL DE SERVIÇO

Sony CorporationSony Brasil LtdaPublicado por Engenharia da Qualidade

Brazilian Model

© 2006.04

Ver. 1.0 04.2006

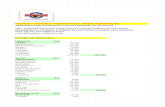

ESPECIFICAÇÕES

CDX-GT707DX

AmplificadorSaídas: Saídas para alto-falantesImpedância do alto-falante: 4 – 8 ohmsSaída de potência máxima 52 W × 4 (a 4 ohms)

GeralSaídas Terminal de saída de áudio (frontal/traseiro)

Terminal de saíida do subwoofer (mono)Terminal de controle de antena elétricaTerminal de controle do amplificador de potência

Entradas Terminal de controle de telefone ATT Terminal de controle de iluminaçãoTerminal de entrada de controle BUSTerminal de entrada de audio BUS/AUX INTerminal de entrada do controle remotoTerminal de entrada da antena

Loudness +8 dB at 100 Hz+0 dB at 10 kHz

• As seções de Sintonizador e CD não requere os ajustes.

Reprodutor de CDRelação sinal/ruído 120 dBResposta de freqüência 10 – 20,000 HzWow e flutter Abaixo do limite mensurável

RádioFMFaixa de sintonia : 87.5 – 107.9 MHzIntervalo de sintonia FM: 200 kHzTerminal de antena: Conector de antena externaFreqüência intermediária 10.7 MHzSensibilidade útil 9 dBfSeletividade 75 dB at 400 kHzRelação sinal/ruído 67 dB (estéreo), 69 dB (mono)Distorção harmônica a 1 kHz

0.5% (estéreo), 0.3% (mono)Separação 35 dB a 1 kHzResposta de freqüência 30 – 15,000 Hz

AM Faixa de sintonia 530 – 1,710 kHzTerminal de antena: Conector de antena externaFreqüência intermediária 10.7 MHz/450 kHzSensibilidade 30 µV

Auto-rádio FM estéreo/AMcom toca-discos a laser

– Continua na próxima saída –

Photo: CDX-GT700D

Modelo que utiliza mecanismo similar Novo

Tipo do mecanismo de CD MG-611WD-186//Q

Modelo da Unidade Otica KSS1000E

Instruções doAcrobat Reader

19 19CDX-GT707DX

CDX-GT707DX

4-1. DIAGRAMA EM BLOCOS — SEÇÃO CD —

SEÇÃO 4DIAGRAMAS

83RFO

RF AMP,DIGITAL SERVO,DIGITAL SIGNAL PROCESSOR

IC2

X80111.2896MHz

89 RFEQO

3RFRP

6TEI

88 RFIRFRPI

2 RFZI

7 TEZI

9 F0O

PD1

PD2

E

F

I-V A

MP

PD LD

DETECTOR

81AGCI82

94

96

95

97

98

TNI

FPI1

FNI1

FPI2

FNI2

TPI

<VRO>

91 LDO 92MDI

(FOCUS)

(TRACKING)

2-AXIS DEVICE

OPTICALPICK-UP BLOCK

(KSS1000E)

• Signal Path: CD PLAY

: FM

LASER DIODE

M

M

M

18

17

VO3–

VO3+

14

13

VO1+

VO1–

12

11 VO2–

VO2+

10

9

VOL+

VOL–FWD

REV

1

28

OPIN4– 26OPIN4+ 27

OPOUT4 25

10 TROOPIN3– 23OPIN3+ 24

OPOUT3 22

12 FMOOPOUT1 4

13 DMOOPOUT2 7

MUTE 21

BIAS 20

16

15

VO4–

VO4+

M903(LOADING)

M901(SPINDLE)

M902(SLED)

FOCUS/TRACKING COIL DRIVE,SLED/SPINDLE/LOADING

MOTOR DRIVEIC1

51PIO348PIO036MSTBY58ZDET37/RST43/CCE42BUCK(CLK)41BUS3(SI)

FL

RL

SUB

A-L

MAIN SECTIONA

62AOUT1 (P07)63BCK (P08)

27 DEC_SSTBY15 CD_ZDET14 CD_XRST13 CD_XCCE

64

22 56 5 72726LRCK (P09)

53 MEC_SELFSW

45 MEC_INSW

42 MEC_LIMIT

12 CD_BUCK11 CD_BUS3

40BUS2(SO) 10 CD_BUS239BUS1 8 CD_BUS138BUS0 7 CD_BUS0

81 X1

80 X0

MEC LOAD43

DRVON6

MEC EJECT44

CDSYSTEM CONTROL

IC3

+1.5V REGIC6

SYSTEM CONTROLIC303 (1/3)

D/A, A/D CONVERTERIC801 LPF

IC471

37 DEC_XMUTE

SDIN0 AUXL157AUXR1BCLK0 R-CH

LRCLK0

33 MCLKI

40 DVDD

30 VDRIVE

47 DVDD

30 DEC_INT

SW2(SELF)

46 MEC_DSWSW1(DOWN)

SW3(DISC IN)

SW4(LIMIT)

56UNISI25RXD57UNISO

58UNICKI50BUS_ON51BU_IN75RSTX

61XFLASH & EJECT_OK

67MECON_CHK

1CDON_1500MV1.5V_ON

63MECON64CDON66ZMUTE

60A_ATT

26TXD

PD1

E

F

VC

VC

VC

LOAD

LD

MON OUT

FCS+

FCS–

TRK+

TRK–

PD2

AUTOMATICPOWER

CONTROLQ21

+1.5V ON/OFFSWITCH

Q2,3

SWITCHINGDRIVER

Q651,652

• R-ch is omitted due to same as L-ch.

24

23X2

16.934MHzX1

12MHz

XI

XO

MAIN SECTIONB

EJECT_OK

UNI SI

UNI SO

ATT59LINKOFF LINK OFF

UNI CLKBUS ONBU CHKSYS RST

47

CD_ON

VOUT

49CDM_ON48

Z_DET

CD+6V

50

68CDON_CHK

15 VDD3CE

+3.3V SWITCHINGREG.IC650

IN BATT1

BATT

51 VCC

4OUT

CD+3.3V

+1.5V

+3.3V

+1.7V REG.Q801+3.3V

+1.5V

BU+3.3V

84

100

58 3 1VOUT1

60VOUT3

72VINL173VINR1

59VOUT2 R-CH

R-CH

(Page 20)

(Page 20)

2020CDX-GT707DX

CDX-GT707DX

4-2. DIAGRAMA EM BLOCOS — SEÇÃO PRINCIPAL —

1 ANT

10

DATA

IN/OUT SELECT,ELECTRIC VOLUME

IC401

PJ501(ANTENNA)

TUX501(TUNER UNIT)

POWER AMP/MULTIPLE VOLTAGE REGULATOR

IC201

SYSTEM CONTROLIC303 (2/3)

AMPIC474

CNP101

PJ401(2/2)

CN401

9

CLK

R-CH (FRONT)R-CH (REAR)

BATT

14 L-OUT

6 AUX-L-IN

5 AUX-L-GND4 AUX-R-GND2 FIL

3 AUX-R-IN

13 R-OUT

TU-R

TU-L43

10VCC11TU_VDD15E2P_VDD

13TU_SCL14TU_SDA

67

S_METER

16

TU_MUTE

E2P_SCL17E2P_SDA

UNI SOUNI SI

UNI CLK

ATTLINK OFF

BU CHK

BUS ON

SYS RST

RESETSTBY

83 VSM21 TUNER ATT

23 EECKO (TU)22 EESIO (TU)

AUDIO+8.3VTU+5VBU+3.3V

LR

4342

MUTE41

GROUNDSWITCH

Q408

R-CH

L

R 35

37

SUB-OUT

RL-OUT

36FL-OUT

R-CH

R-CH

53

OUT-FL+OUT-FL–

OUT-RL+OUT-RL–

97

2927

6

SW1 (AMP_REM)

R-CH

SW2 (ANT_REM)

VP220VP1

35VP (REG) BATT

3037

REG1 (AUDIO+B)REG2 (BU5V)

3133

REG3 (SERVO)REG4 (DR+B)

34REG5 (ILL)

TU+5V

3839

FR-OUTRR-OUT

2 SDA

AUDIO+8.3VB_UP+5VCD+3.3VCD+6VILL+B

4 SCL

SDASCL

22 STB25 DIAG

AUDIO+8.3V

15

13

7

10

12

4

11

16

19

2

3

56

SCLSDA

SCLSDA

27I2C_CKO28I2C_SIO

D904 D906

25ATT4140

AMP_STBAMP_DIAG

16 AC GND20BEEP

58BU_IN

54TESET_IN

11 IN-RLFL+FL–

RL+RL–

FR+FR–RR+RR–

AMP-RANT-R

ACC

TEST

12 IN-FL

MUTEQ470

MUTEQ171

MUTEQ181

MUTE CONTROLQ401,402

56SYSRESET57BUS_ON5UNI_CKO4UNI_SI

3UNI_SO

10 B CHK13 RESET12 BUS ON11 CLK IN8 DATA OUT9 DATA IN

3BATT

4CLK6DATA I/O

456

3

8

7

21

52ACC_INACC CHECK

Q102

TU+5V REGQ501

BU+3.3V B_UP+5V+3.3V REGIC301

BATT

TH100BATT

CNP102(BUS CONTROL IN)

ATT53TEL_ATTTEL ATTENATION SWITCH

Q103

R-CH

R-CH

F901

D120

D121

L

R

AUDIO OUTREAR

L

R

AUDIO OUTFRONT

L

R

SUB OUT(MONO)

CD SECTION A

CD SECTIONB

DISPLAY SECTIONC

BATT

14ILL51ILL_IN

ILLUMINATION CHECKQ907

OVER VOLTAGEDETECT

Q101

BUS INTERFACEIC110

1BUS ON

2RST

D301

D128

(BUS AUDIO IN)PJ401(1/2)

BUS ONSWITCH

Q110,111,112

26 BUS/AUX29 E_VOL_SO/TX31 E_VOL_CKO30 E_VOL_MUTE/RX

PRE AMPIC402

19OUT(RL)

3OUT(FL)

17 RL+

5 FL+

D105

D104

LINE AMPIC470

D401

3 1

12 14

1 3

10 8

A-L16 SUB-INSUB33 RR-INR-CH31 RL-INRL32 FR-INR-CH30 FL-INFL

• Signal Path• R-CH is omitted due to same as L-CH.

: FM

: MW/LW

: BUS AUDIO

(Page 19)

(Page 19)

(Page 21)

21 21CDX-GT707DX

CDX-GT707DX

4-3. DIAGRAMA EM BLOCOS — SEÇÃO DISPLAY —

T620DC-DC

CONVERTERTRANSFORMER

DC-DCCONVERTER

IC620

D623,624

D620,621

D622

FL+4.3V

BATT

BATT1

FL+1V

FL+55V

X30132.768kHz

REMOTECONTROLSIGNAL

RECEIVERIC903

EEPROMIC802

9

8

11

13

84

9899

85

5586

10

FL DISPLAY DRIVEIC901

FL900FLUORESCENT

INDICATORTUBE

KEY_IN0

DISP SI/RXDISP SO/TX

LAT_TA2_OUT

FL_DAT1FL_DAT2FL_DAT3

FL_CLK_IN

KEY_IN1

88 KEY_ACK089 KEY_ACK187 KEY_ACK2

FL+3.3V

Q624

S302(FRONT PANEL DETECT)

BU+3.3V

FLD_ON

RC_IN1RC_IN0

RESET

1 SIRCS

EESIO (DSP)EECKO (DSP)

2 IN 1OUT

2OUT

5SDA6

3635SCL

XCOUT

XCIN

XOUT

XIN

X3026MHz

S303RESET

3029

SYS_SISYS_SO

93DISP_CE 1 SYS_CE

LAT

SI1SI2SI3CLK

GCP_TA4_INBK_TA3_OUT

GCP_TA0_OUT

100DISP CKO 31 SYS_CLK

90DISP_RESET 10 RESET

1 RESETIC904

ILL+B

91NOSE_SW

92DOOR SW

73FSW OUT

2FSW-IN

72FL_ON

74FLD_ON

95DOOR_IND

LED911–921,923–925LSW903(1/2)–913(1/2)

LED931,932

CN902

BU+3.3V

RESET

STBY

KEY MATRIXS900–905,906(2/2),

907–911LSW903(2/2)–913(2/2)

SYSTEM CONTROLIC303 (3/3)

78 RE_A77 RE_B

X9016.75MHz

ROTARY ENCODERS906(1/2)

VOL/PUSH SOUND

S901Z

RESETIC302

CNJ101(REMOTE IN)

LED DRIVEQ134,601

24 12

33 699 53 435

FL_CLK_IN 5

FL_CLK_OUT 100

7

282219

XOUT 11

XIN 13

MAIN SECTION C

FL B+SWITCH

Q301,302

POWERCONTROLQ623,Q642

SWITCHINGDRIVEQ620

DC-DCCONVERTER

CONTROLQ621,622

7 4

1

5VCC

OUT

IN

CT

D907

GCP11BK13

(Page 20)

2222CDX-GT707DX

CDX-GT707DX

• NOTA PARA PLACAS DE CIRCUITO IMPRESSO E DIAGRAMAS ESQUEMÁTICOS

ESTA NOTA É COMUM PARA PLACAS DE CIRCUITOIMPRESSO E DIAGRAMAS ESQUEMÁTICOS.(Em adição a isto, a nota necessária e impressaem cada bloco.)

Para Diagramas Esquemáticos.Nota:• Todos capacitores estão em µF ou descrito diferente. (p: pF)

50 WV ou menos não são indicados exceto para eletrolíticose tântalos.

• Todos resistores estao em Ω e 1/4

W ou a menos de outraforma especificada..

• f : componente interno• C : designacao do painel

Para Placas de Circuito Impresso.Nota:• X : Peças tiradas do lado do componente• Y : Peças tiradas do lado do condutor.• a : Furo vasado.• : Lado da trilha que nao e vista.(As demias trilhas não são indicadas.)

• A : B+ Line.• B : B– Line.• H : adjustment for repair.• Tensões e formas de ondas são DC em relação à terra

sob condições de sem sinal.• Seção menanismo do CD (1/2), (2/2) Sem Indicação : CD PLAY• Seções Principal e Display (1/4), (2/4), (3/4), (4/4) Sem Indicação : FM/MW

< > : CD PLAY∗ : Impossível de Medição

• As tensões são medidas com VOM (Impedância de 10 MΩ).As variações de tensões podem ser notadas devido a tolerâncias.

• As formas de ondas são medidas com um osciloscópio.As variações de tensões podem ser notadas devido atolerâncias normais de produção.

• Números com um circulo referem-se a formas de onda.• Simbologia.

J : CD PLAYF : FMf : MW/LWL : BUS AUDIO

Caution:Pattern face side: Parts on the pattern face side seen from the(Side B) pattern face are indicated.Parts face side: Parts on the parts face side seen from the(Side A) parts face are indicated.

Q

C

Esses são omitidos

EB

EEsses são omitidos

CB

CEsses são omitidos

BE• FORMAS DE ONDAS

— Placa SERVO —(CD PLAY)

— Placa PRINCIPAL —

4-4. LOCALIZAÇÃO DAS PLACAS DE CIRCUITO

Placa PRINCIPAL

Placa SUB

Placa SENSORPlaca SERVO

Placa Display

tSintonizador(TU1)

1 IC2 5 (FEI)

Approx.1Vp-p0 V

0.6 Vp-p

16.9344 MHz

Approx. 100 mVp-p

50 mV/DIV, 5 msec/DIV

0.5 V/DIV, 0.5 µsec/DIV

2 IC2 6 (TEI)

200 mV/DIV, 5 msec/DIV

6 IC2 oh (FPI2), oj (FPI1)

0.5 V/DIV, 0.5 µsec/DIV

Approx. 400 mVp-p

3 IC2 wd (XI)

0.2 V/DIV, 0.2 µsec/DIV

7 IC3 ia (X1)

0.5 V/DIV, 0.2 µsec/DIV

1.1 Vp-p

12 MHz

4 IC2 ia (RFI)

0.5 V/DIV, 0.5 µsec/DIV

5 IC2 of (FNI2), og (FNI1)

1.5 Vp-p

1.5 Vp-p

0 V

1 IC901 qa (XOUT)

3.0 Vp-p

1 V/div, 50 nsec/div

6.747 kHz

— Placa Display —

11 Vp-p

6 IC620 4 (OUT)

5 V/div, 1 µsec/div

2.97 µsec

3.2 Vp-p

10 Vp-p

11.2896 MHz

3 IC650 4 (OUT)

4 IC303 9 (XCOUT)

5 V/div, 1 µsec/div

2 IC801 ed (MCLKI)

1 V/div, 50 nsec/div

2.7 Vp-p

1 V/div, 10 µsec/div

32.768 kHz

2.1 Vp-p

8.664 MHz

1 IC551 0 (XT0)

1 V/DIV, 50 nsec/DIV

3.6 Vp-p

6 MHz

5 IC303 qa (XOUT)

1 V/DIV, 50 nsec/DIV

3 µsec

Nota:Os componentes identificadosipela marca 0 ou linha ponti-lhada são críticos para a segu-rança. Substitua somente pornúmero especificado.

2424CDX-GT707DX

CDX-GT707DX

4-6. DIAGRAMA ESQUEMÁTICO — SEÇÃO MECANISMO DO CD (1/2) —

(Page 25)

R14 R15

IC6

R132

R133

C10

TP21

TP22

TP28

TP29 TP30

TP42

TP45

TP46

C39

R41

R40

R39

R38 R27

R25

R26

R24

R23

R22

TP33

TP32

TP37

TP36

R58

TP39

TP38

TP47

TP48

TP41

TP35

TP34

R42

TP50

TP49TP23

TP24

TP25

TP26

TP27

TP52

TP31

R18

C14

TP51

R57

R55

TP53

IC2

C12

C13

C17

C56

C54

C24

C55

C51

C50

C53

C47

C49

C46

C22C2

0

R28

FB2

FB3C31

C30

R36R30

C42

C41

C72

C60

C43

C58

R29 R19

C132

C80

C133

C26

C25

C32

C33

R33

R31

R32

R34

C36

TP43

TP44

C29

C23

C40 R37

Q2

Q3

C15 R43

C44R44

C45

R53

R52

R54

C18

C48

C52

C19

R13

R12 C16

R16

R11

C11

FB4

CN1

X2

Q21

R35

R20

R48

R47

R46

25 25CDX-GT707DX

CDX-GT707DX

IC B/D

R73

R72

R71

R83

TP67

TP68

TP69

TP72

TP63

TP64

TP65

R85

R77

R68

R67

R69

R60

R61

R62

R79

R80

R81

R82

R84

R70

R9

TP15

TP14

TP1

TP2

TP3

TP4

TP5

TP6

TP7

TP8

TP9

TP10

TP11

TP71

TP61

TP62

R63

R64

R65

R21

TP12

TP13

TP74

TP75

TP76

TP77

TP78

TP79

TP80

TP81

TP82

TP83

TP84

TP85

TP86

TP87

TP88

TP89

TP90

TP91

TP92

TP97

TP98

TP99

BP60

BP10

C69

C70

C68 C66

C62

C71

SW3

SW2

SW4

SW1

M901

M902

M903

C7

IC1

R96

R74

R87

TP70

R75

R97

R98

R8

R5

R6

R2

R1

C67

R78

X1

R86

R88

CN2

R142

R145

R143

IC3

4-7. DIAGRAMA ESQUEMÁTICO — SEÇÃO MECANISMO DO CD (2/2) —

(Page 30)

(Page 24)

2828CDX-GT707DX

CDX-GT707DX

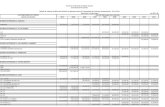

4-9. DIAGRAMA ESQUEMÁTICO — SEÇÃO PRINCIPAL (1/4) —

(Page 29)

(Page 31)(Page 30)

IC B/D

IC B/D

IC B/D

IC B/D

R50

4

R52

2

R52

1

R485

R501

R50

2

FB50

2

R481

R479

R478

R480

R864

R85

4

R658

C651 C655

D65

1

R860R858

R853

R657

R476

R470

R472

R471R475

R473

D501

D652

C885

R46

1

R46

2

R859 R851

C882

C881

R661

C854

C865

C871

R656

C172

C182

C272

C282

C410

L651

L652

C482

C479C481

C480

C857

C434

R663

R45

1

R45

2

R45

3

R45

4

R45

5

C455

C456

C457

C458

C459

D653

L801

R556R555

C474

C476

C472

C471

C469

C477

C473

C884

C883

C868

C860C859

C856

C852

X801

FB801

C409

C408

C433

L655 L654 L653Q651

C654

R664

C815

C867

C866

R810 R809 R808 R807

C814C813C812C811

R811

R812

C817

C816

R802

C802

R801

C820

C850

C822

IC471

C478

R477

R474

IC472

C421

C422

C423

R420

C424

IC401

R498

L401

IC470

C475

C419 C420

R411 R410

C417 C418

R405 R404

R487

R488

R484

L800

R852

R863

C855

C853

R861

C851

R659

R660R862 Q

652

R869

R868

C872

R655

C652

R654C653

R855 C858C863 C862 C864 C861

Q501

C510 FB501

C513

C544 C5

09

L503

C501C502

R505

JR609

R599

PJ501

R483

R557

X551

C559

C560

FB551

C557 R553

R554C558

FB552 C553 C561

C554C555

C556

IC551

TUX501

Q380

R380

R551

R552

C552

C551

Q552

Q551

C514

C470

IC801

C870

C869

Q801

R662

C656

IC650

29 29CDX-GT707DX

CDX-GT707DX

IC B/D

IC B/D

C203R201

R106

R105

R104

R110

R109

R402

D121

D120

R112

D118

R929

R922

R424

R403

R406

D113

D116

D117

D111

D110

D114

D115

R408

D909

Q402

R184

R174

R274

D402

R143

R434

R185

R284

R243

R275

R423

R175

R432

R285

CN401

C403

R430

C173

C183

C273

C283

FB402

R207

C437

C440

D112

C208

C209

C216

C217

C439

C438

C231

C201

C207

C219

C218

C206C236

C238

C239

C237

C227C210C215

C232

C229

C491

C142 C242

C288

C188

C178

C278

C442

R921

R920

R108

R107

C107

Q281

Q271

Q401

D401

R401

C401

R202 C202

C204

R204

R206

R205

R203

R407

Q181

Q171

Q470

C412

C443

C228 C205

R409

C411

C430

IC474

R433

C441C436

R431R429

R436

R435

C400

C226

C225

C214

C223

C221

C212

C211

D119

R142

R242

D109

R103

C102

C903

R111

D108

D106

PJ401

F901

Q408

Q103

Q907

Q102

C431

IC402IC201

CNP101

L101

C103

4-10. DIAGRAMA ESQUEMÁTICO — SEÇÃO PRINCIPAL (2/4) —

(Page 28)

(Page 30) (Page 31)

3030CDX-GT707DX

CDX-GT707DX

R33

8

R33

9

R34

3

R34

4

R34

5

R35

0

C326

R337

R33

6

R35

1

R33

3

CNP301

C303

C311

R364

R367

R335

JR618

R32

3

R857

X301

R306

C333

D301X302

C334

FB328

C306C304

C331

C886

R356

R332

R357

C316

C315

C328

C317

L303

C327

S303

S302

JR608

IC301

C321

C332

IC302

C313

R334

R309

R342

D907

JR607

C318

TP9

R372

R325

R373

R856

R38

2

R38

1

R365R366

R34

6

R32

2

R31

4

L301

FB334

FB333

FB332

FB335

C302C301

C305

FB329

D906

D904

IC802

IC303

R363

R361

R360

R313 R31

2 R30

2

R30

3

R377

D322

R33

1

R34

7

C322

C323

R307

R321

R310

R311

R324

R320

4-11. DIAGRAMA ESQUEMÁTICO — SEÇÃO PRINCIPAL (3/4) —

(Page 25)

(Page 28) (Page 29)

(Page 31)

31 31CDX-GT707DX

CDX-GT707DX

IC B/D

IC B/D

C101

R115

R119

R114

R633

C621

R116

R319R318

R626

C622

C112

D622

D623

R630

R629

D62

0JR

615

D624

D10

3

D10

1

D10

2

D104

D105

D128

C625 R644

C624

R621 R620

R625L304

R623

R622

D630

TH100

R101

R102

C340C341

C342

JR605JR602 JR606

IC620

IC110Q111

Q110

CNP102

CNJ101JR613

R636

C629

R637

JR604

C628Q622

Q621

R632 D626

R631

D625

R628

R627

C626

Q623

Q642

Q302

Q301

C620

R624

L620

C111C110R127R126

R118R117

Q112

Q101

Q620

C623

D621

R601

R602

R603

Q134

Q601

D851

D850

D849

D848

D847

D846

CNVSS

ILL

D845

D844

D842

C520

R845

C633

D841

D840

L502 L520

CN701

D843

JR621

JR603

T620

Q624

4-12. DIAGRAMA ESQUEMÁTICO — SEÇÃO PRINCIPAL (4/4) —

(Page 28) (Page 29)

(Page 30)

(Page 34)

3434CDX-GT707DX

CDX-GT707DX

FB90

4

FB917

FB911

LAT_

TA2_

OUT

BK_T

A3_O

UT

FB918

FB919

R981

D912

D902 D901

D904

D908

D907

D920

R948

C929

R970

C905

R982

C928

FB92

0

FB90

2

FB90

3

R956

R958

R955

C919

C915

R960 R961

C921

C902

R964R963

C920

R96

2

R950

FB912

FB913

FB914

FB915

FB916

R951

R952

R953

R925 R926 R927 R928

C927

C925

C926

R929 R930

R937 R938 R939 R940

R901

R902

R903

R904

R905

R906

R907

R908

R909

R910

R921

R920

R919

R918

R917

R916

R915

R914

R913

R912

R942 R943

R932R931 R933 R936R935R934

R941

R944

S906

LSW913(1/2)

S909

S908LSW909(1/2)

LSW908(1/2) S907

LSW912(1/2)LSW907(1/2)

LSW906(1/2)

LSW905(1/2)

LSW904(1/2) S905

LSW903(1/2) S904

S911 LSW911(1/2)

S903

LSW910(1/2)S910

S902

C903

IC903

R974

FB908

R971

CN902

IC904

R959

X901

R954

FB905

FB921 FB901

JC902

C901

IC901

S901R990

R992D990

D991

LED921

LED924

LSW910(2/2)

LED923 LSW909(2/2)

LSW907(2/2)

LSW905(2/2)

LSW908(2/2)

LSW906(2/2)

LSW904(2/2)

LSW903(2/2)

LED925

LED912

LED918

LED911

LED917

LED913

LED914

LED915

LED916

LSW911(2/2)

LSW912(2/2)

LSW913(2/2)

LED920

FL900

CNP501

LED931 LED932

LED919

(GT700D) (GT705DX)

5152535455565758

25242322212019181716151413121110987654321

5960616263646566676869707172737475

4-15. DIAGRAMA ESQUEMÁTICO — SEÇÃO DISPLAY —

(Page 31)

35

CDX-GT707DX

• DIAGRAMAS EM BLOCOS DO IC

IC801 ADAU1421YSTZ (Placa PRINCIPAL (1/4))

20

27 28 29 30 31 32 33 34 35 36 37 38 39 40262524232221

19181716151413121110987654321

60

76 75

FILTAVOUT3

59 VOUT258 VOUT157 AUXR156 AUXL155 AVDD354 HPR53 HPL52 A-GND

51 A-GND50 PLL_LF49 AVDD248 D-GND

47 DVDD46 RESETB

45 PWM444 PWM3

43 PWM2PWM142

41 D-GND

VREFA-GNDAVDD1

NCNCNCNCNCNCNCNC

D-GND

D-GND

DVDD

SDIN

0SD

IN1

SDIN

2SD

IN3

LRCL

K0VI

NL4

VINL

3

VINL

2

VINR

4

VINR

3

VINR

2

VINL

1AV

DD5

AVDD

4FI

LTD

AUXR

2AU

XL2

VOUT

4

NC NC NCA-GN

DA-

GND

VINR

1

IDAC

BCLK

0

D-GN

D

ODVD

DVD

RIVE

D-VD

DD-

GND

MCL

KIM

CLKO

BCLK

1LR

CLK1

SDO0

SDO1 NC

DVDD

DVDDI2C_AD0

SYNCHRONIZEMULTI-CHANNELDIGITAL INPUT

SRCASYNCHRONIZEDIGITAL INPUT

PLLSYSTEMCLOCKS

I2C_SDAI2C_SCL

NCNC

I2 C IN

TERF

ACE

A-VSYNC DELAY

MEMORY

PROG

RAM

MAB

LEAU

DIO

PROC

ESSO

RCO

RE

ADC

MULTI-CHANNNELDIGITAL OUTPUTS

DAC

74 73 72 71 70 69 68 67 66 65 64 63 62 6177787980

DAC

DAC

DAC

36

CDX-GT707DX

IC650 NJM2379V (Placa PRINCIPAL (1/4))

IC1 BA5968FP-E2 (SERVO Board (2/2))

8 7 56

VREF

OSC

0.52V

30µA

L.O

PWMER.AMP

S.C.P

U.VLO

IN F.B

GN

D

OU

T

REF

CT CS VCC

1 2 43

1

2

11

13

14

12

LEVELSHIFT

LEVELSHIFT

LEVELSHIFT

LEVELSHIFT

MUTE

FWD

FWD

LDCTL

NC

OPOUT1

NC

NC

OPOUT2

POWVCC VCCVOL–

VOL+

VOL2–

VOL2+

VO1–

VO1+

REV

OPIN4+

OPIN4–

OPOUT4

OPIN3+

OPIN3–

OPOUT3

MUTEVOL+GND

VOL3–

VOL3+

VOL4–

VOL4+

REV

OUTR OUTF

10

98

7

6

5

28

27

26

25

24

23

22

212019

18

17

16

15

4

3

37

CDX-GT707DX

VDDA

INTERPOLATOR

RAMBUFFER

&CONTROL

LOGIC

TEST LOGIC&

PIN MUX'S

I2C/SPI

INTERFACE

BAND PASSFILTER

SIGMA DELTACONVERTER

SINC4FILTER

REF3

REF2

REF1

VSS

VDDD

RESETN

TM

1

MPX16

CSNSDAOUT

RDSREG

3

INTN

MPX

SINC

4REG

SDAINSCKSPITESTREG

14

2

3

4

5

6

7

8

INTN15

SA_DATAOUT13SDA_DATAIN12SCL_CLK11

OSCILLATOR

XTO10

XTI9

RDSDEMODULATOR &

SYNCHRONIZATION

2

1

2

3

6

5

4

17

18

19

20

7

10

15

16

12

11

14

13

8

9

LIFT AMP

LIFT AMPCIN (L)

OUT (RL)

RL-

RL+

VCC

RR+

RR-

OUT (RR)

CIN (R)

GND (R)

COUT (R)

OUT (FR)

FR-

FR+

REF

FL+

FL-

OUT (FL)

COUT (L)

GND (L)

SIGNAL AMP

FRONT-RIGHT REAR-RIGHT

FRONT-LEFT REAR-LEFT

SIGNAL AMP

SIGNAL AMP SIGNAL AMP

IC551 TDA7333013TR (Placa PRINCIPAL (1/4))

IC402 NJM2792V (Placa PRINCIPAL (2/4))

38

CDX-GT707DX

IC401 BD3426K-E2 (Placa PRINCIPAL (1/4))

33

1 2 3 4 7 8 9 10 11

38

39

40

41

42

43

44

12

1314

15

16

17

18

19

20

21

22

32 31 30 29 28 27 26 25 24 23

RR-IN

SUB-OUT

FL-OUT

RL-OUT

FR-OUT

RR-OUT

VCC

MUTE

CLK

DATA

DGND

VCC/2

FR-IN

RL-IN

FL-IN

NC NC ADJ

BP31

BP21

BP11

BP12

AGND FI

L

AUX-

R-IN

AUX-

L-IN

CD-C

-R

CD-C

-L

TU-R

TU-L

AUX-

R-GN

D

AUX-

L-GN

D

2 W

IRE

SERI

ALCO

NTRO

L LO

GIC

DUAL MODE INPUT SELECTOR(3 SINGLE STEREO INPUT AND 1 GROUND ISOLATION INPUT)

+15dB~-32dB 1dB/STEP-32dB~-46dB 2dB/STEP-46dB~-78dB 4dB/STEP-∞

INPUT GAIN 1(0~+20dB)

BPFGENERAL PURPOSE

(+20~-20dB/2dB STEP)

SCF BASE & TREBLE(+20~-20dB/2dB STEP)

VOLUME(0~-72dB, -∞dB)LOUDNESS

LOUDNESSON/OFF

VCO

MUTE

FADER

5 6

INPUT GAIN 2(0~+20dB)

1CH

1CH

1CH

2CH

2CH

2CH

1CH2CH

FADER

37 FADER

36

35

FADER

FADER

34FADER

BP22

BP32

SUB-IN

L-OUTR-OUT

39

CDX-GT707DX

IC201 TDA8588AJ/N2/R1 (Placa PRINCIPAL (2/4))

MUT

EM

UTE

ENABLELOGIC

STANDBYMUTE

CHIP DETECTDIAGNOSTIC

PROTECTIONDIAGNOSTIC

SWITCH

REGU

LATO

R

SWITCH

REFERENCEVOLTAGE

LOADDUMPPROTECTION

TEMPERATUREPROTECTION

BACK-UPSWITCHREGULATOR

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

TAB

OUT FL-

OUT FL+

OUT RL-

OUT RL+

INRL

SGND

INRR

OUT RR+

OUT RR-

OUT FR+

OUT FR-

DIAG

SW2(ANT REM)

SW1(ANT REM)

REG3(SERVO)

REG4(DR+B)

VP(REG)

REG2(BU 5V)

SDA

SCL

VP2

PGND3

SVR

INFL

INFR

AC GND

PGND2

VP1

STB

PGND1

RST

CRES

REG1(AUDIO +B)

GND(REG)

REG5(ILL)

CBU

FL

RL

RR

VP

FR

I2C BUS

40

CDX-GT707DX

IC620 NJM2377M(TE2) (Placa PRINCIPAL (4/4))

8 7 56

VREF

OSC

0.52V

30µA

L.O

PWMER.AMP

S.C.P

U.VLO

IN F.B

GN

D

OU

T

REF

CT CS VCC

1 2 43

IC110 BA8271F-E2 (Placa PRINCIPAL (4/4))

1

2

3

456

7 8

9

10

14

131211

BUS ONSWITCH

RESETSWITCH

BATTERYSWITCH

BUS ON

RST

BATT

CLKVREF

GND

VCC

RSTBUS ONCLK-INB-CHK

DATA IN

DATA OUT

DATA I/O

41

CDX-GT707DX

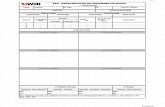

• DESCRIÇÕES DOS PINOS DE IC• IC3 MB90486BPFV-G-177E1 (CD SYSTEM CONTROL) (PLACA SERVO (2/2))

Pin No. Pin Name I/O Pin Description

1 CDON_1500MV O Servo 1.5 V power supply control signal output

2 to 5 NC — Not used. (Open)

6 DRVON O Motor drive mute signal output

7 CD_BUS0 I/O Bus data input/output 0

8 CD_BUS1 I/O Bus data input/output 1

9 VSS — Ground

10 CD_BUS2 I/O Bus data input/output 2

11 CD_BUS3 I/O Bus data input/output 3

12 CD_BUCK O Bus clock signal output

13 CD_XCCE O Chip enable signal output

14 CD_XRST O Reset signal output

15 CD_ZDET I Zero detection signal input

16 to 20 NC — Not used. (Open)

21 VCC — Power supply pin (+3.3 V)

22 DAC_ZDETL I Not used. (Pull down)

23 DAC_ZDETR I Not used. (Pull down)

24 NC — Not used. (Open)

25 RXD I UART RXD data input (MCBUS/Flash data input)

26 TXD O UART TXD data output (MCBUS/Flash data output)

27 DEC_SSTBY O SRAM STANDBY mode control signal output

28, 29 NC — Not used. (Open)

30 DEC_INT I Request signal input

31, 32 NC — Not used. (Open)

33 AVCC — Power supply pin (+3.3 V) for A/D converter

34 AVRH — External reference voltage for A/D converter

35 AVSS — Ground

36 NC — Not used. (Open)

37 DEC_XMUTE O Mute signal output L: mute

38, 39 NC — Not used. (Open)

40 VSS — Ground

41 NC — Not used. (Open)

42 MEC_LIMIT I Sled limit in detection switch signal input

43 MEC_LOAD O Loading motor signal output (Load direction)

44 MEC_EJECT O Loading motor signal output (Eject direction)

45 MEC_INSW I Pack-in detection signal input

46 MEC_DSW I Chucking end detection switch signal input

47, 48 MD0, MD1 I CPU operation mode designation signal input (Connected to Vcc.)

49 MD2 I CPU operation mode designation signal input (Connected to Vss.)

50 BUS_ON I Bus on signal input L: bus on

51 BU_IN I Backup power supply detect signal input

52 NC I Not used. (Open)

53 MEC_SELFSW I Disc insert detection switch signal input L: disc in interruption

54, 55 NC — Not used. (Open)

56 UNISI I Control bus serial data input

57 UNISO O Control bus serial data output

58 UNICKI I Control bus serial clock input

59 LINKOFF O Bus link off signal output

60 A_ATT O Audio mute signal output H: mute on

42

CDX-GT707DX

61 XFLASH&EJECT_OK I Front panel open signal input H: eject

62 OPEN_REQ O Front panel open/close request signal output Not used in this set.

63 MECON O Mechanism deck power supply control signal output

64 CDON O Servo power supply control signal output

65 XUART I S-Bus/MC-Bus change signal input H: S-Bus, L: MC-Bus

66 ZMUTE O Zero detection mute signal output

67 MECON_CHK I CD +6V power rising detection signal input

68 CDON_CHK I CD +3.3V power rising detection signal input

69 to 74 NC — Not used. (Open)

75 RSTX I System reset signal input

76 NC — Not used. (Open)

77 X1A — Not used. (Open)

78 X0A — Connected to Vss

79 VSS — Ground

80 X0 I Main-clock INPUT (12 MHz)

81 X1 O Main-clock OUTPUT (12 MHz)

82 VCC — Power supply pin (+3.3 V)

83 XWD I Connected to Vss

84 XINIT3 I Not used. (Open)

85 NC — Not used. (Open)

86 XSJIG I Not used. (Open)

87 to 89 XINIT0 to 2 I Not used. (Open)

90 to 96 NC — Not used. (Open)

97 XDES I Destination setting pin

98 XLINE I Not used. (Open)

99, 100 NC — Not used. (Open)

Pin No. Pin Name I/O Pin Description

43

CDX-GT707DX

• IC303 M30622MWP-328GP (SYSTEM CONTROL) (PLACA PRINCIPAL (3/4))

Pin No. Pin Name I/O Pin Description

1 SIRCS I Remote control data signal input

2 FSW-IN I FL DC-DC converter frequency count input

3 UNI_SO O Control bus serial data output

4 UNI_SI I Control bus serial data input

5 UNI_CKO O Control bus serial clock output

6 BYTE I Not used (Connect to ground)

7 CNVSS I Not used Fixed at “L”

8 XCIN I Sub clock signal input (32.768 kHz)

9 XCOUT O Sub clock signal output (32.768 kHz)

10 RESET I Reset signal input

11 XOUT O Main clock signal output (6 MHz)

12 VSS — Ground

13 XIN I Main clock signal input (6 MHz)

14 VCC1 — Power supply pin (+3.3 V)

15 NMI I Non-maskable interruption signal input Fixed at “H”

16 NC — Not used (Open)

17 DAVN I RDS data block synchronization detection signal input

18 TUNER ATT-IN I Tuner attenuation zero cross input

19 NS-MASK O Tuner noise detect mask signal output

20 BEEP O Beep signal output

21 TUNER ATT O Tuner mute signal output

22 EESIO(TU) I/O Tuner pack EEPROM data signal input/output

23 EECKO(TU) O Tuner pack EEPROM clock signal output

24 NC — Not used (Open)

25 ATT O Line mute signal output

26 BUS/AUX O Bus audio/AUX exchange signal output

27 I2C_CKO O I2C serial transfer clock output

28 I2C_SIO I/O I2C serial data input/output

29 E_VOL_SO O E-VOL serial data output

30 E_VOL_MUTE O E-VOL mute signal output

31 E_VOL_CKO O E-VOL serial transfer clock output

32 DSP_RESET O DSP reset signal output

33 DSP_I2C_SIO I/O DSP I2C data input/output

34 DSP_I2C_CKO O DSP I2C serial transfer clock output

35 EECKO (DSP) O EEPROM serial transfer clock output

36 EESIO (DSP) I/O EEPROM serial data input/output

37 DSP_ON O DSP power supply on signal output

38 NC — Not used (Open)

39 HOLD I Not used Fixed at “L”

40 AMP_DIAG I Amplifier self-diagnostic test function signal input

41 AMP_STB O Amplifier standby signal output

42 NC — Not used (Open)

43 NC — Not used (Open)

44 WRI/WR I External data bus (WRI/WR) input Fixed at “H”

45 NC — Not used (Open)

46 NC — Not used (Open)

47 EJECT_OK O Eject OK signal output

48 CDM_ON I Mechanism deck power supply ON signal input

49 CD_ON I Servo power supply ON signal input

44

CDX-GT707DX

50 Z_DET I Zero detection mute signal input

51 ILL-IN I Illumination check signal input

52 ACC_IN I Accessory check signal input

53 TEL_ATT I Telephone mute signal input

54 TEST_IN I Test mode signal input

55 RC_IN1 I Remote control signal input 1

56 SYSRESET O System reset signal output

57 BUS_ON O BUS ON signal output

58 BU_IN I Backup power supply detection signal input

59 NC — Not used (Open)

60 VCC2 — Power supply (+3.3 V)

61 NC — Not used (Open)

62 VSS — Ground

63 NC — Not used (Open)

64 NC — Not used (Open)

65 NC — Not used (Open)

66 NC — Not used (Open)

67 NC — Not used (Open)

68 NC — Not used (Open)

69 NC — Not used (Open)

70 DST_SEL1 I Destination/setting port signal input 1

71 DST_SEL2 I Destination/setting port signal input 2

72 FL_ON O FL power supply on/off signal output

73 FSW OUT O FL DC-DC converter frequency exchange signal output

74 FLD_ON O FL driver power supply on/off signal output

75 NC — Not used (Open)

76 NC — Not used (Open)

77 RE_B I Rotary encoder signal input B

78 RE_A I Rotary encoder signal input A

79 NC — Not used (Open)

80 NC — Not used (Open)

81 NC — Not used (Open)

82 QUALITY I Tuner noise detect signal input

83 VSM I S-meter voltage signal input

84 KEY_IN0 I Key signal input 1

85 KEY_IN1 I Key signal input 2

86 RC_IN0 I Remote control signal input 0

87 KEY_ACK2 I Key acknowledge signal input 0

88 KEY_ACK0 I Key acknowledge signal input 1

89 KEY_ACK1 I Key acknowledge signal input 2

90 DISP_RESET O Display control reset signal output

91 NOSE_SW I Front panel detect signal input

92 DOOR SW I Front panel open/close signal input

93 DISP_CE O Display control chip enable signal output

94 AVSS — Ground

95 DOOR_IND O DISC IN illumination on signal output

96 VREF — Reference voltage for A/D convert

97 AVCC — Power supply (+3.3 V)

98 DISP SI/RX I Display control serial data signal input

99 DISP SO/TX O Display control serial data signal output

100 DISP CKO O Display control serial transfer clock output

Pin No. Pin Name I/O Pin Description

45

CDX-GT707DX

• IC901 M30876MJB-054GP (FL DISPLAY CONTOROL) (DISPLAY BOARD)

Pin No. Pin Name I/O Pin Description

1 SYS_CE I Chip enable signal input

2 NC — Not used (Open)

3 FL_DAT3 O FL serial data-3 output

4 NC — Not used (Open)

5 FL_CLK_IN I FL serial transfer clock input (Connected to 35,100 pin)

6 BYTE I Connected to ground

7 CNVSS I Flash write port Fixed at “L”

8 NC — Not used (Open)

9 NC — Not used (Open)

10 RESET I Reset signal input

11 XOUT O Main clock signal output (6.75 MHz)

12 VSS — Ground

13 XIN I Main clock signal input (6.75 MHz)

14 VCC1 — Power supply (+3.3V)

15 NMI I Non-maskable interruption signal input Fixed at “H”

16 NC — Not used (Open)

17 NC — Not used (Open)

18 NC — Not used (Open)

19 GCP_TA4_IN I FL BK signal input (Connected to 22 pin)

20 NC — Not used (Open)

21 NC — Not used (Open)

22 BK_TA3_OUT O FL BK signal output (Connected to 19 pin)

23 NC — Not used (Open)

24 LAT_TA2_OUT O FL LAT signal output

25 NC — Not used (Open)

26 NC — Not used (Open)

27 NC — Not used (Open)

28 GCP_TA0_OUT O FL GCP signal output

29 SYS_SO O Display serial data output

30 SYS_SI I Display serial data input

31 SYS_CLK I Display serial transfer clock input

32 NC — Not used (Open)

33 FL_DAT1 O FL serial data-1 output

34 NC — Not used (Open)

35 FL_CLK_IN I FL serial transfer clock input (Connected to 5,100 pin)

36 to 38 NC — Not used (Open)

39 HOLD I External data bus (HOLD) input Fixed at “L”

39 to 43 NC — Not used (Open)

44 WRI/ER I External data bus (WRI/WR) input Fixed at “H”

45 to 59 NC — Not used (Open)

60 VCC2 — Power supply (+3.3V)

61 NC — Not used (Open)

62 VSS — Ground

63 to 93 NC — Not used (Open)

94 AVSS — Ground

95 NC — Not used (Open)

96 VREF I Reference voltage input (Connected to AVCC)

97 AVCC — Power supply (+3.3V)

98 NC — Not used (Open)

99 FL_DAT2 O FL serial data-2 output

100 FL_CLK_OUT O FL serial transfer clock output (Connected to 5,35 pin)