Iram.handouts

Click here to load reader

-

Upload

nadiascarvalho -

Category

Documents

-

view

216 -

download

1

description

Transcript of Iram.handouts

Sistemas de MemóriaConceitos Básicos

João Canas Ferreira

Outubro de ����

Tópicos deArquitetura e Organização de Computadores

Assuntos

Tópicos

� MemóriasAspetos geraisMemórias EstáticasMemórias Dinâmicas

� Descodificação de endereçosOrganização geralDescodificação totalDescodificação parcial

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias

� MemóriasAspetos geraisMemórias EstáticasMemórias Dinâmicas

� Descodificação de endereçosOrganização geralDescodificação totalDescodificação parcial

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias Aspetos gerais

Taxonomia

Registos e bancos de registos permitem guardar pequenas quantidades dedados. Para maiores quantidades, usam-se memórias de acesso direto.

RAM = random access memory (memória de acesso direto): permitem leitura eescrita em qualquer posição.

ROM = read-only memory: permitem apenas leitura.

A maior parte das memórias RAM perde os dados quando é desligada aalimentação (memória volátil). Exceções:

(E)EPROM: (Electrically) erasable programmable ROM

memórias FLASH.

Dois tipos de memórias RAM voláteis:

SRAM: memória estática (cada célula de memória é um “flip-flop”);

DRAM: memória dinâmica (cada célula deve ser atualizada periodicamente).

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias Aspetos gerais

Circuitos de memória: organização conceptual

0

M bits

12

N-1

endereço(linha)

dados(M bits)

Para P linhas de endereço: N = �P

Abreviaturas: ��� = ���� = � K, ��� = ������� = � MO porto de dados é bidirecional: é preciso especificar o tipo de acesso (leituraou escrita).M é a largura da memória.

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias Memórias Estáticas

Memórias estáticasAs memórias estáticas aproximam-se do modelo conceptual de funcionamento.

SRAM 2M x 16 Dout[15:0]

Address[20:0]21

Din[15:0]16

Chip select

Output enable

Write enable

16

‡ Para aceder à memória:ativar o circuito: chip select (CS) ativoespecificar o tipo de acesso:

ativar output enable (leitura) OU write enable (escrita).João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias Memórias Estáticas

Memórias estáticas: acessosTempo de acesso para leitura: intervalo entre o instante em que output enable

e endereço estão corretos e o aparecimento de dados na saída.

Valores típicos para memórias estáticas:rápidas: �–� nstípicas: �–�� ns (cerca de �� milhões de bits)de baixo consumo: �–�� vezes mais lentas

Durante esse tempo, um processador que execute uma instrução por ciclo euse um relógio de � GHz, executa:

�–� instruções��–�� instruções

Tempo de acesso para escrita: endereços e dados devem estar estáveis antese depois do flanco. O sinal de write enable é sensível ao nível (não ao flanco) edeve ter uma duração mínima para que a escrita se realize.

O tempo de escrita é superior ao tempo de leitura.João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias Memórias Estáticas

Memórias estáticas: circuito de saídaBuffer tristate

� estados: �, �, desligado

Sel

InOut

In

InOut

Out

Sel = 1

Sel = 0

Circuito de saída:Select 0

Data 0

Enable

OutIn

Select 1

Data 1

Enable

OutIn

Select 2

Data 2

Enable

OutIn

Select 3

Data 3

Enable

OutIn

Output

‡ Ao contrário de um banco de registos, ocircuito de saída não pode ser baseado nummultiplexador: uma SRAM 64K x 1 precisariade ter um multiplexador �����-para�.

‡ Solução: utilizar buffer tristate, cuja saída podeter � estados (�, � ou alta-impedância).

‡ No estado de alta-impedância, a saída docircuito está desligada.

‡ O estado da saída é determinado por umaentrada de controlo: Sel.

‡ Todas as saídas são ligadas em paralelo. Nãopode existir mais que uma saída ativa (i.e., nãoem alta-impedância) em cada instante.

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias Memórias Estáticas

Estrutura básica de uma memória estática

latch

D

C

Enable

Q

D

0

2-to-4 decoder

Write enable

Din[1]

latch

D

C

Enable

Q

D

Din[1]

Dout[1] Dout[0]

latch

D

C

Enable

Q

D

1

latch

D

C

Enable

Q

D

latch

D

C

Enable

Q

D

2

latch

D

C

Enable

Q

D

latch

D

C

Enable

Q

D

3

latch

D

C

Enable

Q

D

Address

Fonte: [COD�]

SRAM 4x2

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� � / ��

Memórias Memórias Estáticas

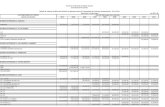

Memórias estáticas organizadas por bancosPara limitar o tamanho do descodificador de endereços:

12

to

4096

decoder

Address

[21–10]

4096

4K x

1024

SRAM

4K x

1024

SRAM

4K x

1024

SRAM

4K x

1024

SRAM

4K x

1024

SRAM

4K x

1024

SRAM

4K x

1024

SRAM

4K x

1024

SRAM

Mux

Dout7

Mux

Dout6

Mux

Dout5

Mux

Dout4

Mux

Dout3

Mux

Dout2

Mux

Dout1

Mux

Dout0

1024Address

[9–0]

Fonte: [COD�]

Organização típica de uma memória 4Mx8 como uma coleção de blocos dememória 4Kx1024.

Os blocos MUX são realizados por buffers de três estados.João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Memórias Memórias Dinâmicas

Memória dinâmica (DRAM)Valor guardado como carga num condensador.

O acesso é feito através de um transístor a operar como interruptor.

Consequência: maior densidade (bit/mm�), logo circuitos de maiorcapacidade e menor custo.

Comparação: SRAM requer � a � transístores por bit armazenado.Acesso a DRAM é feito em duas etapas:

� seleção de coluna (usando uma parte do endereço);

� seleção de linha (usando os restantes bits do endereço).

DRAM é mais lenta que SRAM. Valor típico: � Gibit (512M⇥4), tempo deacesso �� ns.

Condensador vai perdendo a carga e deve ser periodicamente “refrescado”,fazendo uma leitura seguida de escrita (circuito dinâmico). Refrescamento“consome” �% a �% dos acessos.

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Memórias Memórias Dinâmicas

Esquema geral do acesso a uma memória dinâmica

Endereço[10-0]

Descod.

de linhas

11-to-2048

2048 x 2048

matriz

2048 trincos

Mux

Dout

Endereço: ��+�� bits.DRAM 4M⇥1: �� bits selecionam a linha, que é “copiada” para ���� trincos.Multiplexador seleciona uma de ���� entradas.

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Memórias Memórias Dinâmicas

Módulos de memória: DIMMCIs individuais podem ser agrupados em módulos.Ex: módulo 32Mx64 (��� MB) pode usar �� componentes 32Mx4.

Ram0 Ram1 Ram2 Ram14 Ram15

4 4 4 4 4d [3:0]

d [7:4]

d [11:8]

d [59:56]

d[63:60]

a[24:0]

d[63:0]

32Mx4

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Descodificação de endereços

� MemóriasAspetos geraisMemórias EstáticasMemórias Dinâmicas

� Descodificação de endereçosOrganização geralDescodificação totalDescodificação parcial

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

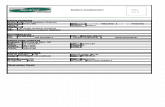

Descodificação de endereços Organização geral

Organização da memória de um computador

A memória física de um computador é geralmente composta por váriosmódulos (circuitos integrados, DIMM, etc.) por forma a ser possível obtermaiores capacidades de armazenamento.

Para além dos módulos de memória é necessário ter um circuito dedescodificação de endereços que seleciona quais os módulos ativos duranteum dado acesso (com base no endereço apresentado pelo CPU).

Organização típica: os bits menos significativos são ligados diretamente aosmódulos individuais, enquanto os bits mais significativos são usados parafazer a seleção dos módulos.

Linhas de dados podem ser “partilhadas” por mais que um módulo (usandobuffers tristate).

Alguns módulos usam internamente esta abordagem.

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Descodificação de endereços Organização geral

Organização da memória: diagrama de blocos

dados[ ]

End. End. End. End.

CS CS CS CSdados dados dados dados

N bitsEnd[N-1:0]

Descodificador

M-N bits de selecçãoEnd[M-1: N]

Endereço tem M bits, dos quais M-N podem serusados na descodificação

N bits de endereço

Apenas uma saídaactiva de cada vez

Para memórias DRAM a descodificação de endereços é mais complicada. Apenas abordaremos ocaso das memórias SRAM.

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Descodificação de endereços Organização geral

Regras para descodificação de endereçosPara que esta organização funcione bem, a descodificação de endereçosdeve garantir que:

Para o conjunto de todos os módulos que partilham uma mesma li-nha de dados: apenas um (ou nenhum) deve ser ativado durante umacesso.

Se esta condição não for respeitada, os componentes podem serdefinitivamente danificados.

O mapeamento de endereços para componentes pode ser classificado deacordo com o número de endereços que é mapeado na mesma posição física:

total: � endereço! � posição

parcial: N endereços! � posição

Na descodificação total, todos os bits do endereço são “usados”: ligadosdiretamente aos componentes ou utilizados na seleção dos componentes.

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

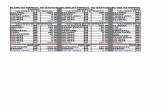

Descodificação de endereços Descodificação total

Descodificação total: exemplo

A[11:0] A[12:0]

CSCS

RAM1 RAM2

8 bits 8 bits

8 bits

A[15:0]

D[7:0]

D[7:0] D[7:0]

&& A[15]A[15]

A[14]A[14]

A[13]A[13]

A[12]

RAM1: 4Kx8 RAM2: 8Kx8Espaço de endereçamento do CPU:64 K, 1 byte por endereço

RAM 1:1011 XXXX XXXX XXXXGama: B000H a BFFFH

RAM2:001X XXXX XXXX XXXXGama: 2000H a 3FFFH

Endereço B712H (�����)!RAM�Endereço C1E0H (�����)! nenhum circuito

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Descodificação de endereços Descodificação parcial

Descodificação parcial: exemplo

A[11:0] A[12:0]

CSCS

RAM1 RAM2

8 bits 8 bits

8 bits

A[15:0]

D[7:0]

D[7:0] D[7:0]

&& A[15]A[15]

A[14] A[13]

RAM1: 4Kx8 RAM2: 8Kx8Espaço de endereçamento do CPU:64 K, 1 byte por endereço

RAM 1:10?? XXXX XXXX XXXXGamas:

8000H a 8FFFH9000H a 9FFFHA000H a AFFFHB000H a BFFFH

RAM2:0?1X XXXX XXXX XXXXGamas:

2000H a 3FFFH6000H a 7FFFH

O byte �� de RAM1 pode ser acedido através de que endereços?800AH, 900AH, A00AH e B00AH

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��

Referências

Referências

COD� D. A. Patterson & J. L. Hennessey, Computer Organization andDesign, � ed.

COD� D. A. Patterson & J. L. Hennessey, Computer Organization andDesign, � ed.

Os tópicos tratados nesta apresentação são descritos na seguinte secção de[COD�]:

apêndice C, secção C.�

Também são tratados na seguinte secção de [COD�]:

apêndice B, secção B.�

João Canas Ferreira (FEUP/DEEC) Sistemas de Memória Outubro de ���� �� / ��