CD1_P2_v2

-

Upload

raymundo-cordero -

Category

Documents

-

view

214 -

download

1

description

Transcript of CD1_P2_v2

Universidade Federal de Mato Grosso do Sul Circuitos Digitais I – P2 Departamento de Engenharia Elétrica

Nome:________________________________________________________________

Q1 (1,5p). Descrever as tabelas de verdade dos flip-flops SR, D e JK, para cada valor de entrada

e saída lógica possível.

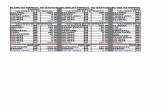

Q2 (2p). Efetuar as seguintes operações (usar números de 8 bits, incluído o bit de sinal. A

resposta deve ser apresentada tanto em formato decimal como binário. Indicar se existe

overflow):

a) 19 – 25 b) (–90) – (–120); c) 127 – 127. d) 123 + 14;

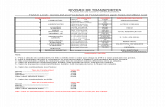

Deve-se usar o seguinte procedimento: a) Converter os decimais em números binários com sinal; b) Efetuar todas as operações matemáticas usando números binários; c) Depois de calcular a resposta em binário, expressar o resultado como número decimal; d) Indicar se aconteceu overflow ou não na operação matemática. Q3 (1.5). A seguinte figura é um somador

bit a bit tipo Full-Adder. Os bits xi e yi são os

bits a somar. O bit ci-1 é o carrier da etapa

da soma binária anterior. Achar as funções

lógicas das saídas ci (carrier para a seguinte

etapa da soma) e si (resultado da soma dos

bits xi e yi). Usar Karnaugh.

Conectar somadores bit a bit tipo Full Adder

para criar um somador de dois números

binários de 3 bits. Podem-se usar também

portas lógicas and, or, not, nand ou nor.

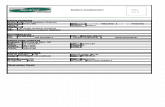

Q4(3.5). Projetar um circuito digital que permita a subtração de dois números de 4 bits com

sinal (X e Y): Z = X – Y. Pode projetar um circuito lógico que calcule diretamente a diferença

entre os números, ou fazer um circuito que ache o complemento de 2 de Y para simplificar os

cálculos. Pode-se usar o bloco somador full adder (FA) da Figura da Q3 como um circuito

integrado conhecido. Podem-se usar circuitos not, and, or, nand, nor, xor, mux, demux,

codificadores ou decodificadores.

Q5(1,5p). Responder as seguintes perguntas

a) Descrever a operação de um registrador de deslocamento (1p).

b) Seja X um número binário de 5 bits (incluindo o bit de sinal). O complemento a 2 do

complemento a 2 de X é igual a X? Comprovar usando X = +5 e X = 3. Todas as

operações matemáticas devem ser efetuadas usando números binários (0,5p).