Apostila_ETR2_Completa

-

Upload

sandra-rocha -

Category

Documents

-

view

266 -

download

10

Transcript of Apostila_ETR2_Completa

1

2012

Antonio Luiz dos Santos Filho

IFSP/Campus Cubatão

Apostila de Eletrônica Básica – Módulo D

Versão

2

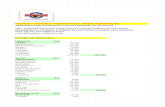

C O N T E Ú D O

Capítulo 7 - Transistor de Efeito de Campo (FET - Field Effect Transistor) .............................................. 12

Famílias de Transistores de Efeito de campo .................................................................................................... 13

Transistor de Efeito de Campo de Junção - JFET ......................................................................................... 13

O JFET Operando na Região Linear ou Resistiva ......................................................................................... 18

o JFET Operando na Região de Pinch-Off ....................................................................................................... 23

O JFET Como Amplificador - Modelo Para Pequenos Sinais e Baixas Frequências ....................... 29

Transistor de Efeito de Campo de Porta Isolada - IGFET ou MOSFET ..................................................... 33

O MOSFET de Indução ............................................................................................................................................ 33

MOS Complementar (CMOS) ................................................................................................................................ 40

O MOSFET de Depleção .......................................................................................................................................... 41

Observações Gerais Sobre os MOSFETs de Indução e de Depleção ..................................................... 44

MOSFETs de Potência .................................................................................................................................................. 45

Transistor Bipolar de Porta Isolada ....................................................................................................................... 46

Capítulo 8 - Amplificadores Operacionais: Fundamentos ................................................................................. 48

Amplificador Diferencial ............................................................................................................................................. 50

Características Importantes de um OPAMP Real ............................................................................................. 51

Ganho de Tensão em Malha Aberta (Ao) ......................................................................................................... 52

Tensão de Offset de Entrada (vio) ....................................................................................................................... 52

Corrente de Polarização de Entrada (IB) ......................................................................................................... 53

Corrente de Offset de Entrada (Ios) .................................................................................................................... 54

Slew Rate (Máxima Taxa de Variação do Sinal de Saída - SR) ................................................................ 54

Produto Ganho x Banda Passante (GBW - Gain x Band Width) ............................................................. 55

Tensão Diferencial de Entrada (VID) ................................................................................................................. 56

Faixa Permitida de Tensões de Entrada (VI) ................................................................................................. 56

Máxima Excursão do Sinal de Saída (VOM) ...................................................................................................... 56

Drift (Desvio) .............................................................................................................................................................. 56

Amplificador Operacional Ideal ............................................................................................................................... 58

Princípios Fundamentais na Análise de Circuitos com OPAMPs Ideais ............................................. 59

Circuitos Utilizando Amplificadores Operacionais ..................................................................................... 60

Capítulo 9 - Aplicações Lineares dos Amplificadores Operacionais .............................................................. 61

Amplificadores com OPAMPs ................................................................................................................................... 61

Amplificador Inversor ............................................................................................................................................. 61

Amplificador Somador Inversor ......................................................................................................................... 63

3

Amplificador Não-Inversor ................................................................................................................................... 64

Seguidor de Tensão ou Buffer Analógico ....................................................................................................... 64

Amplificador Subtrator ou Diferencial............................................................................................................. 65

Amplificadores de Instrumentação ................................................................................................................... 66

Integração e Derivação em Circuitos Elétricos ............................................................................................. 68

Amplificador Integrador Inversor ..................................................................................................................... 68

Amplificador Diferenciador Inversor ............................................................................................................... 71

Conversores de Sinal .................................................................................................................................................... 72

Conversor de Corrente para Tensão ................................................................................................................. 72

Conversor de Tensão para Corrente ................................................................................................................. 73

Reguladores de Tensão .......................................................................................................................................... 74

Filtros Ativos ................................................................................................................................................................... 76

Filtro Passa-Baixas Ativo com Amplificador Operacional ....................................................................... 77

Filtro Passa-Baixas Ativo com Amplificador Operacional ....................................................................... 77

Filtro Passa-Faixa Ativo com Amplificador Operacional .......................................................................... 78

Filtro Rejeita-Faixa Ativo com Amplificador Operacional ....................................................................... 79

Capítulo 10 - Aplicações Não-Lineares dos Amplificadores Operacionais ................................................ 80

Comparadores de Tensão ........................................................................................................................................... 80

Circuitos Integrados Especiais Para Uso Como Comparadores ............................................................. 82

Detetor de Janela ....................................................................................................................................................... 84

Detetor Para Quatro Níveis de Tensão ............................................................................................................. 86

Disparador de Schmitt (Schmitt Trigger) ....................................................................................................... 86

Amplificadores Não-Lineares ................................................................................................................................... 89

Amplificador Logarítmico ..................................................................................................................................... 89

Amplificadores Exponenciais............................................................................................................................... 90

Retificadores Ativos ...................................................................................................................................................... 91

Retificador Ativo de Meia-Onda .......................................................................................................................... 92

Retificador Ativo de Onda Completa ................................................................................................................. 93

Detetor de Pico ........................................................................................................................................................... 94

Capítulo 11 – Osciladores com Circuitos Integrados ........................................................................................... 95

Osciladores Harmônicos ............................................................................................................................................. 96

Oscilador Harmônico Ponte de Wien Usando Operacional ..................................................................... 98

Oscilador Harmônico por Deslocamento de Fase (Phase Shift) ......................................................... 100

Oscilador Phase Shift Utilizando Amplificador Operacional ................................................................ 101

Oscilador Harmônico de Quadratura com Operacional ......................................................................... 102

4

Osciladores de Relaxação ........................................................................................................................................ 103

Multivibrador Astável com OPAMP ................................................................................................................ 103

Gerador de Ondas Triangulares e Quadradas ............................................................................................ 105

O Circuito Integrado 555 ......................................................................................................................................... 107

Operação do 555 Como Multivibrador Astável ......................................................................................... 108

Operação do 555 Como Temporizador (“Multivibrador” Monoestável - “One-Shot”) .............. 110

Capítulo 12 – TIRISTORES ........................................................................................................................................... 113

SCR - Retificador Controlado de Silício .............................................................................................................. 113

Métodos de Disparo de um SCR ....................................................................................................................... 114

Comutação de um SCR ......................................................................................................................................... 119

Aplicações do SCR ....................................................................................................................................................... 120

Utilização do SCR em Regime de Tensão Contínua e Constante......................................................... 121

Utilização do SCR com Tensão Contínua Pulsante (Tensão Senoidal Retificada) ....................... 125

TRIAC - Triodo de Corrente Alternada .............................................................................................................. 127

Curva Característica de um TRIAC .................................................................................................................. 129

Comutação de um TRIAC .................................................................................................................................... 130

Circuitos de Disparo Para Tiristores .................................................................................................................. 130

Circuito Resistivo ................................................................................................................................................... 130

Circuito Capacitivo ................................................................................................................................................ 132

Circuitos de Disparo com Dispositivos de Resistência Negativa ........................................................ 133

Circuitos de Disparo Usando Circuitos Integrados Especiais .............................................................. 140

Circuitos de Disparo com Atuação On/Off................................................................................................... 145

5

Í N D I C E D E F I G U R A S

Figura 7-1 – Estrutura Interna e Simbologia dos JFETs Canal N e Canal P ................................................. 13

Figura 7-2 – Polarização de um JFET Canal N ......................................................................................................... 14

Figura 7-3 – Corrente de Dreno de um JFET em Função da Tensão Entre Dreno e Source ................. 15

Figura 7-4 – Comportamento do JFET Para Tensões VGS Diferentes de Zero .......................................... 16

Figura 7-5 – Detalhamento do Limite Entre as Regiões Linear e de Pinch-off de um JFET ................. 17

Figura 7-6 – Detalhamento da Região Linear de Operação de um JFET Canal N ..................................... 18

Figura 7-7 - JFET Utilizado em Controle Automático de Ganho ...................................................................... 20

Figura 7-8 - Circuito Básico de Chaveamento com JFET e Respectivas Formas de Onda ..................... 21

Figura 7-9 – JFET Como Chave em Paralelo ............................................................................................................ 22

Figura 7-10 – Diagrama Básico de Multiplexador Analógico Utilizando JFET .......................................... 22

Figura 7-11 – Curva de Transferência de um JFET Operando na Região de Pinch-off .......................... 23

Figura 7-12 – Limites para as Curvas de Transcondutância de um JFET .................................................... 25

Figura 7-13– Polarização Independente para o Gate e Efeito da Variação dos Parâmetros do JFET

................................................................................................................................................................................................................... 25

Figura 7-14 – Circuito de Autopolarização e Efeito da Variação dos Parâmetros do JFET .................. 26

Figura 7-15 – Polarização com Divisor de Tensão e Efeito da Variação dos Parâmetros do JFET .. 28

Figura 7-16 – Modelo para Pequenos Sinais de um JFET................................................................................... 29

Figura 7-17 – Modelo Alternativo para Pequenos Sinais de um JFET ......................................................... 31

Figura 7-18 - Estrutura dos MOSFETs de Indução com Canal N e Canal P ................................................. 33

Figura 7-19 - Formação do Canal pela Tensão entre o Gate e o Substrato num NMOS de Indução . 34

Figura 7-20 – Curvas Características de Transferência e de Saída para um NMOS de Indução ........ 35

Figura 7-21 – Símbolos Mais Comuns para o NMOS de Indução .................................................................... 36

Figura 7-22 – Símbolos Mais Comuns para o PMOS de Indução ..................................................................... 36

Figura 7-23 – Circuito de Polarização Fixa para um NMOS de Indução ...................................................... 37

Figura 7-24 - Circuito de Polarização Autopolarizante para um NMOS de Indução............................... 38

Figura 7-25 - Circuito de Polarização com Divisor de Tensão No Gate para um NMOS de Indução 39

Figura 7-26 – Estrutura Básica de um Dispositivo CMOS .................................................................................. 40

Figura 7-27 – Circuito Lógico com Célula CMOS e Circuito Equivalente para vi = “0” e vi = “1” ....... 40

Figura 7-28 - Estrutura dos MOSFETs de Depleção com Canal N e Canal P ............................................... 41

Figura 7-29 - MOSFET de Depleção de Canal N nos Modos de Indução e de Depleção ......................... 42

Figura 7-30 - Curvas Características de Transferência e de Saída para um NMOS de Depleção ....... 43

Figura 7-31 – Símbolos Mais Usados para Representar o Nmos e o PMOS de Depleção ...................... 43

Figura 7-32 - Estrutura, Símbolo e Circuito Equivalente de um IGBT .......................................................... 46

Figura 8-1 – Diagrama em Blocos de um Amplificador Operacional Genérico ......................................... 48

Figura 8-2 – Diagrama Interno de Um Amplificador Operacional Simples ................................................ 49

Figura 8-3 – Símbolo do Amplificador Operacional, Aspecto Físico e Conexões ..................................... 49

Figura 8-4 – Amplificador Diferencial Polarizado por Fonte de Corrente Constante ............................ 50

Figura 8-5 – Técnica de Compensação da Tensão de Offset de Entrada de um OPAMP Real ............. 52

Figura 8-6- Técnicas para a Compensação Externa da Tensão de Offset de Entrada ............................ 53

Figura 8-7 – Efeito das Correntes de Polarização de Entrada de um OPAMP Real ................................. 53

Figura 8-8 – Efeito do Slew Rate Sobre o Sinal de Saída de um OPAMP Real ............................................ 54

Figura 8-9 – Relação entre Ganho de Tensão e Banda Passante num OPAMP Real................................ 55

6

Figura 9-1 – Diagrama Básico do Amplificador Inversor com OPAMP ........................................................ 61

Figura 9-2 – Diagrama do Amplificador Somador Inversor com OPAMP ................................................... 63

Figura 9-3 – Diagrama do Amplificador Não-Inversor com OPAMP ............................................................. 64

Figura 9-4 – Obtendo um Buffer Analógico a Partir de um Amplificador Não-Inversor ...................... 64

Figura 9-5 – Exemplo Prático de Utilização do Seguidor de Tensão com OPAMP................................... 65

Figura 9-6 – Diagrama Básico do Amplificador Subtrator ................................................................................ 65

Figura 9-7 – Subtrator Utilizado Para Processar o Sinal de uma Ponte de Wheatstone ....................... 66

Figura 9-8 – Diagrama Básico de um Amplificador de Instrumentação ...................................................... 67

Figura 9-9 – Diagrama Básico de um Integrador Inversor com Operacional ............................................ 68

Figura 9-10 – Circuito Prático de Integrador com Operacional ...................................................................... 70

Figura 9-11 – Circuito Integrador com MOSFET para a Descarga do Capacitor ...................................... 70

Figura 9-12 – Diagrama Básico de um Diferenciador Inversor com Operacional ................................... 71

Figura 9-13 – Circuito Prático de Diferenciador com Operacional ................................................................ 71

Figura 9-14 – Influência da Resistência Interna de uma Fonte de Corrente ............................................. 72

Figura 9-15 – Diagrama Básico de um Conversor Corrente-Tensão ............................................................. 72

Figura 9-16 – Conversor de Tensão Para Corrente Usando OPAMP ............................................................. 73

Figura 9-17 – Conversores Tensão-Corrente com Transistor Bipolar ......................................................... 74

Figura 9-18 – Regulador de Tensão Usando Amplificador Operacional...................................................... 74

Figura 9-19 – Regulador de Tensão com Proteção Contra Sobrecorrente ................................................. 75

Figura 9-20 – Aspecto Físico e Símbolo de um CI Regulador de Tensão com Três Terminais ........... 75

Figura 9-21 – Curvas de Resposta dos Diversos Tipos de Filtro ..................................................................... 76

Figura 9-22 – Filtro Ativo Passa-Baixas Não-Inversor ........................................................................................ 77

Figura 9-23 – Filtro Ativo Passa-Altas Não-Inversor ........................................................................................... 77

Figura 9-24 – Filtro Ativo Passa-Faixa Não-Inversor .......................................................................................... 78

Figura 9-25 – Método para a Implementação de um Filtro Rejeita-Faixa .................................................. 79

Figura 10-1 – Diagrama Básico de um Comparador de Tensões com OPAMP.......................................... 80

Figura 10-2 – Diagrama Básico de um Comparador Inversor ......................................................................... 81

Figura 10-3 – Comparador com Níveis de Tensão de Saída com Módulos Diferentes .......................... 81

Figura 10-4 – Saída do Tipo Coletor Aberto e Ligação do Resistor Externo .............................................. 83

Figura 10-5 – Pinagem dos Circuitos Integrados da Família X39 ................................................................... 83

Figura 10-6 – Pinagem da Família X11 e Circuito de Aplicação Usando o Terminal de Strobe ......... 84

Figura 10-7– Diagrama Básico de um Detetor de Janela e Comportamento do Seu Sinal de Saída . 85

Figura 10-8 – Implementação de Detetor de Janela Usando Operacionais Convencionais ................. 85

Figura 10-9– Detetor de Janela com Quatro Níveis de Referência ................................................................. 86

Figura 10-10 – Transições Espúrias na Saída de um Comparador, Devidas à Presença de Ruído ... 87

Figura 10-11 – Diagrama Básico de um Disparador de Schmitt ..................................................................... 87

Figura 10-12 – Curva de Transferência de um Disparador de Schmitt ........................................................ 88

Figura 10-13 - Diagrama, Curva de Transferência e Equações de um Schmitt Trigger Não-inversor

................................................................................................................................................................................................................... 88

Figura 10-14 – Diagrama Básico de um Amplificador Logarítmico com Operacional ........................... 89

Figura 10-15 – Amplificador Inversor Logarítmico Realimentado com Transistor Bipolar ............... 90

Figura 10-16 – Diagramas Básicos de Amplificador Exponencial com Operacional .............................. 90

Figura 10-17 – Efeito da Tensão de Limiar de um Diodo Sobre os Sinais Retificados........................... 91

Figura 10-18 – Diagrama de um Retificador Ativo de Meia-Onda ................................................................. 92

Figura 10-19 – Diagrama Aperfeiçoado de Retificador Ativo de Meia-Onda............................................. 92

7

Figura 10-20 – Diagrama de um Retificador Ativo de Onda Completa ........................................................ 93

Figura 10-21– Diagrama Básico e Formas de Onda de um Detetor de Pico com OPAMP .................... 94

Figura 10-22 – Detetor de Pico com Buffer de Saída e Circuito de Reset .................................................... 94

Figura 11-1 – Princípio de Operação de um Oscilador Harmônico ............................................................... 96

Figura 11-2 – Efeito do Produto dos Ganhos Sobre o Sinal de Saída do Oscilador Harmônico ......... 97

Figura 11-3 – Duas Diferentes Representações do Oscilador Ponte de Wien Básico com OPAMP .. 98

Figura 11-4 – Diagramas de Oscilador Ponte de Wien com Estabilização de Amplitude ..................... 99

Figura 11-5 – Diagramas Básicos dos Osciladores por Deslocamento de Fase ..................................... 100

Figura 11-6 – Oscilador Phase-Shift com Amplificador Operacional ......................................................... 101

Figura 11-7 – Oscilador por Deslocamento de Fase com Estabilização de Amplitude ....................... 101

Figura 11-8 – Oscilador de Quadratura com Amplificadores Operacionais ........................................... 102

Figura 11-9 – Gráfico dos Sinais de Saída vo1 e vo2 .......................................................................................... 103

Figura 11-10 – Diagrama de um Multivibrador Astável com OPAMP ....................................................... 103

Figura 11-11 – Formas de Onda num Multivibrador Astável com OPAMP ............................................. 104

Figura 11-12 – Diagrama e Formas de Onda Num Gerador de Ondas Triangulares e Quadradas 105

Figura 11-13 – Oscilador com Limitação de Amplitude Usando Diodos Zener ..................................... 106

Figura 11-14 - Diagrama em Blocos e Aspecto Físico de Diversos Encapsulamentos do C.I. 555 . 107

Figura 11-15 – Tabela-Verdade de um Flip-Flop RS ......................................................................................... 108

Figura 11-16 – Diagrama de um Multivibrador Astável com o CI 555 ...................................................... 108

Figura 11-17 – Formas de Onda Principais de um Multivibrador Astável Usando o CI 555 ............ 109

Figura 11-18 – Diagrama do Multivibrador Monoestável (Temporizador) com o CI 555 ................ 110

Figura 11-19 – Formas de Onda num Temporizador em Função dos Pulsos de Entrada ................. 111

Figura 12-1 – Estrutura Interna, Simbologia e Aspectos Físicos de um SCR .......................................... 113

Figura 12-2 – Mecanismo de Disparo de um SCR Através de Aplicação de Corrente no Gate......... 114

Figura 12-3 – Curva Característica de um SCR .................................................................................................... 115

Figura 12-4 – Símbolo E Estrutura do Retificador Controlado de Silício Foto-Ativado ..................... 117

Figura 12-5 – Mecanismo de Disparo por Variação de Tensão .................................................................... 118

Figura 12-6 – Exemplos de Redes Amortecedoras ............................................................................................ 118

Figura 12-7 – Símbolos para um GTO ..................................................................................................................... 119

Figura 12-8 – Circuito de Chaveamento com SCR e Seu Equivalente com Chave Comum ................ 121

Figura 12-9 – Dois Métodos Para Permitir a Comutação do SCR ................................................................ 122

Figura 12-10 – Circuito de Chaveamento Utilizando o Método de Comutação Forçada ................... 122

Figura 12-11 – Circuito Equivalente Após o Disparo do SCR Principal .................................................... 123

Figura 12-12 – Mecanismo de Comutação Forçada do SCR Principal ....................................................... 123

Figura 12-13 – Tensão Sobre a Carga em Função dos Pulsos de Disparo dos SCRs ............................ 124

Figura 12-14 – Influência do Intervalo Entre os Disparos Sobre o Ciclo de Trabalho ........................ 124

Figura 12-15 – Utilização do SCR em Regime Senoidal, Sem e Com Retificação Prévia ..................... 125

Figura 12-16 – SCR Como Interruptor (com Retificação Prévia da Tensão de Entrada) ................... 125

Figura 12-17 – Utilização do SCR Como Controlador de Potência .............................................................. 126

Figura 12-18 – Ligação Antiparalela de Dois SCRs ............................................................................................ 128

Figura 12-19 – Simbologia e Estrutura Interna de um TRIAC ...................................................................... 128

Figura 12-20 – Quadrantes de Disparo de um TRIAC ...................................................................................... 129

Figura 12-21 – Curva Característica de um TRIAC ............................................................................................ 130

Figura 12-22 – Circuitos Resistivos Para o Disparo de Tiristores............................................................... 131

Figura 12-23 – Circuito de Disparo Capacitivo Para SCR ................................................................................ 132

8

Figura 12-24 – Curva Característica de um Dispositivo Unilateral de Resistência Negativa ........... 133

Figura 12-25 – Diagrama Genérico de um Oscilador de Relaxação com DRN ........................................ 134

Figura 12-26 – Formas de Onda no Oscilador de Relaxação com DRN ..................................................... 134

Figura 12-27 – Estrutura, Símbolo, Circuito Equivalente e Aspecto Físico de um UJT ....................... 135

Figura 12-28 – Oscilador de Relaxação com UJT ................................................................................................ 136

Figura 12-29 – Estrutura Interna e Simbologia de um DIAC ......................................................................... 137

Figura 12-30 – Diagrama de um Oscilador de Relaxação Utilizando DIAC ............................................. 138

Figura 12-31– Circuito com Sincronismo Direto com a Rede e Algumas Formas de Onda .............. 138

Figura 12-32 – Circuito Para Controle de Potência Sobre Cargas AC ........................................................ 139

Figura 12-33 - Circuito de Controle de Potência com Dupla Rede RC, Filtro e Amortecedor .......... 140

Figura 12-34 – Pinagem e Diagrama em Blocos do Circuito Integrado TCA785 ................................... 141

Figura 12-35 – Influência do Pino 12 Sobre a Duração dos Pulsos de Disparo ..................................... 143

Figura 12-36 – Circuito de Disparo Típico Utilizando o CI TCA785 ........................................................... 144

Figura 12-37 – Circuito de Disparo Foto-Ativado .............................................................................................. 146

9

Informações Úteis

1) Ementa do Curso: O conteúdo programático será dividido em unidades, a saber:

• Transistores de Efeito de Campo

• Amplificadores Operacionais

• Osciladores com Amplificadores Operacionais e com o Circuito Integrado 555

• Tiristores.

Esse programa será desenvolvido conforme a capacidade de absorção da Turma e de acordo com

a duração do Módulo, podendo, eventualmente, não ser ministrado em sua totalidade.

Ao final de cada unidade será dada uma Lista de Exercícios, que poderá ser resolvida

individualmente ou por grupos de até quatro alunos.

2) Provas Escritas: Serão realizadas 2 Provas Escritas, compostas das seguintes seções:

• Laboratório: Essa seção vale 2 pontos e conterá de 1 a 3 questões referentes aos experimentos de Laboratório realizados até a data da Prova. Nessa seção não há possibilidade de escolha das questões a serem resolvidas nem de seu valor.

• Parte Discursiva: Essa seção vale 3 pontos e conterá 5 questões, das quais o aluno deverá

responder 3, escolhidas a seu critério. O aluno também poderá escolher o valor de cada questão,

desde que, simultaneamente: a soma dos valores atribuídos às três questões escolhidas seja igual

a 3 pontos, nenhuma delas receba valor maior do que 2 pontos, e nenhuma delas receba valor

inferior a 0,5 pontos.

• Parte de Cálculos e Análise: Essa seção vale 5 pontos e conterá 4 questões, das quais o aluno

deverá resolver 3, escolhidas a seu critério. O aluno também poderá escolher o valor de cada

questão, desde que, simultaneamente: a soma dos valores atribuídos às três questões escolhidas

seja igual a 5 pontos, nenhuma delas receba valor maior do que 2 pontos, e nenhuma delas receba

valor inferior a 1 ponto.

Qualquer situação diferente das acima descritas, seja no que se refere ao número de questões

respondidas em cada seção da prova, seja no que se refere aos valores atribuídos às questões, será

resolvida a critério exclusivo do professor. O conteúdo das Provas Escritas será o mesmo coberto pelas

duas últimas Listas de Exercícios realizadas anteriormente. Após cada duas Listas de Exercícios será

realizada uma Prova Escrita. Assim, a divulgação do gabarito da 2ª e da 4ª Lista de Exercícios serve,

respectivamente, como aviso quanto à realização da 1ª e da 2ª Prova Escrita.

3) Prova Substitutiva: De acordo com as Normas Acadêmicas do Curso, o aluno que faltar num dia de

Prova tem direito a realizar uma Prova Substitutiva, desde que requeira tal direito junto à CAE, num

prazo máximo de 48 horas após a realização da prova perdida. Esse direito cobre apenas a perda de uma

prova, ou seja, o aluno que perder as duas provas poderá fazer apenas uma substitutiva. Essa prova

poderá ser aplicada, a critério do Professor, fora do horário normal das aulas, ou ao final do módulo, na

aula imediatamente anterior à realização do Processo Final de Avaliação. Ressalta-se que a Prova

Substitutiva é dada apenas aos alunos que tiverem perdido uma prova, e não àqueles que fizeram a prova

e foral mal sucedidos.

10

4) Recuperação Paralela: Será proporcionado ao aluno que tiver nota inferior a 6,0 em qualquer das 2

Provas Escritas um processo paralelo de recuperação. Esse processo será realizado através da inclusão

em cada Prova (com a óbvia exceção da primeira) de questões referentes à prova anterior. As questões

de recuperação paralela terão seu valor medido em porcentagem. 20% serão referentes a duas questões

discursivas, 20% serão referentes a uma ou duas questões de Laboratório e os 60% restantes serão

referentes a uma questão de cálculo e/ou análise. O aluno que obtiver 100% nessas questões terá o valor

da nota da prova anterior alterado para 6. Para porcentagens inferiores, a nota será alterada de modo

proporcional.

5) Orientações Sobre os Relatórios de Experimentos Práticos: Os Relatórios dos experimentos devem

ser redigidos em conformidade com os princípios estudados em Metodologia do Trabalho Científico,

devendo conter: uma breve introdução teórica a respeito do assunto (não será aceita uma mera

transcrição da apostila), os requisitos de projeto (quando houver), o diagrama do circuito, a memória de

cálculo, os valores efetivamente utilizados, explicação sobre o procedimento experimental, resultados

obtidos (descrições, gráficos, tabelas, etc.). O item mais relevante é a comparação entre os resultados

obtidos e aqueles previstos pela teoria. Isso deve incluir os cálculos teóricos e comentários explicando as

razões para eventual discrepância e as conclusões decorrentes da realização do experimento. Os

Relatórios devem incluir também as referências bibliográficas consultadas. Obviamente, nem todos esses

itens serão aplicáveis a todos os experimentos. Deve ser entregue um relatório por grupo de trabalho

(bancada) e o prazo para a entrega é até a realização do próximo experimento, a menos que especificado

em contrário pelo professor.

6) Critério de Avaliação: A Nota do Componente Curricular (NCC) do curso será obtida através da

fórmula: NCC =P1 + P2

2fffffffffffffffffff

, onde P1 é a Nota da 1ª metade do Módulo e onde P2 é a Nota da 2ª metade do

Módulo.

A nota da Nota da 1ª metade do Módulo será obtida pela fórmula:

P1 =5BPV 1 + 3BMR1 + 2BML1

10fffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffff, onde PV1 é a nota da 1ª Prova Escrita, MR1 é a média das notas dos

Relatórios das experiências de Laboratório referentes à primeira parte da matéria e ML1 é a média das

notas das Listas de Exercícios referentes à primeira parte da matéria.

A nota da Nota da 2ª metade do Módulo será obtida pela fórmula:

P1 =5BPV 2 + 3BMR2 + 2BML2

10ffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffff, onde PV2 é a nota da 2ª Prova Escrita, MR2 é a média das notas dos

Relatórios das experiências de Laboratório referentes à parte final da matéria e ML1 é a média das notas

das Listas de Exercícios referentes à parte final da matéria. Eventual arredondamento de nota será

realizado apenas após o cálculo da Nota do Componente Curricular.

Como se pode notar pelo critério exposto acima, metade da Nota do Componente Curricular se

refere a atividades individuais (Provas Escritas) e a outra metade se refere a atividades em grupo

(Relatórios de Experiências de Laboratório e Listas de Exercícios).

Alunos com NCC ≥ 5,75 (valor que é arredondado para 6,0) estarão aprovados na disciplina e

alunos com NCC < 3,75 (que é arredondado para 4,0) estarão retidos. Nesses dois casos, a Média Final

será igual à Nota do Componente Curricular.

11

7) Processo Final de Avaliação (PFA): Os alunos que obtiverem Nota do Componente Curricular

inferior a 6 (seis) e igual ou superior a 4 (quatro) poderão participar do Processo Final de Avaliação

(PFA), a ser realizado na última semana do módulo. O PFA consistirá de uma terceira Prova Escrita

abrangendo toda a matéria do Módulo e que será composta por 4 questões discursivas, cada uma valendo

0,5 (meio ponto), num total de 2,0 (dois pontos); por 4 questões de cálculo e/ou análise, cada uma

valendo 1,5 (um ponto e meio), num total de 6,0 (seis pontos); e 2 questões de Laboratório, cada uma

valendo 1,0 (um ponto), num total de 2,0 (dois pontos). Não haverá nessa prova escolha de questões a

serem resolvidas nem de seus valores. A Média Final será o maior valor entre a Nota do Componente

Curricular e a nota obtida no Processo Final de Avaliação.

Note-se que a Recuperação Paralela da 2ª Prova Escrita será realizada em conjunto com o PFA.

Se, por acaso, a nota obtida após a recuperação for suficiente para a aprovação do aluno, o PFA será

desconsiderado.

8) Apostila: O curso é baseado na presente apostila, e sua impressão é fortemente recomendada. O

aluno deverá acompanhar as aulas tendo em seu poder a apostila. A princípio, as únicas anotações

necessárias se referem à resolução dos Exemplos Numéricos que serão propostos durante as aulas, além

de correções de eventuais erros presentes no texto.

9) Devolução e Guarda dos Trabalhos: Todos os trabalhos realizados ao longo do Curso (Listas de

Exercícios, Relatórios e Provas Escritas) serão devolvidos aos alunos após sua correção. Essa devolução

será feita durante o horário oficial de aulas e, se o aluno não estiver presente, o trabalho será entregue ao

Representante da Turma ou ao seu vice. Os trabalhos deverão ser cuidadosamente guardados até o

encerramento do módulo, para comprovação no caso de notas não lançadas ou lançadas com erro. Tais

retificações serão feitas exclusivamente mediante a apresentação do trabalho correspondente, antes da

data estipulada para a entrega dos resultados finais à Secretaria.

10) Resultado Final: Realizadas todas as atividades previstas neste documento e calculada a Média Final

de acordo com o exposto nos itens 4 e 5 deste documento, não caberá qualquer recurso junto ao

professor para que a Média Final seja alterada (realização de prova-extra, trabalho-extra, etc.). Isso deve

estar bem claro para o aluno, a fim de que sejam evitadas situações constrangedoras para si mesmo e

para o professor.

11) Bibliografia Recomendada: A apostila que serve como base para o Curso possui o conteúdo

estritamente necessário. As fontes de referência mais completas são livros, que abrangem um número

maior de tópicos e, em geral, com maior profundidade. Um único livro pode servir como referência para

várias disciplinas do Curso. Portanto, sempre que possível, os livros devem ser adquiridos.

Recomendam-se as seguintes obras, listadas em ordem crescente de complexidade:

a. Eletrônica (2 volumes) – Autor: Malvino – Editora Makron Books

b. Eletrônica (2 volumes) – Autores: Millmann e Halkias – Editora Makron Books

c. Microeletrônica – Autores: Sedra e Smith – Editora Pearson Education

Todas essas obras estão disponíveis na Biblioteca da Escola.

12) Site: O material referente ao curso (Apostila, Listas de Exercícios, Resolução de Listas e Provas, etc.)

estará disponível no site www.prof-antonio-luiz.webnode.com.

12

CAPÍTULO 7 - TRANSISTOR DE EFEITO DE CAMPO (FET -

FIELD EFFECT TRANSISTOR)

No estudo sobre o transistor bipolar de junção, vimos que a condução de corrente elétrica nesse

dispositivo se dá por meio de dois tipos de portadores de carga elétrica: os elétrons livres e as lacunas,

sendo essa a razão para o adjetivo “bipolar”.

Existe, entretanto, um tipo de transistor no qual apenas um dos tipos de portadores é responsável

pela condução da corrente, sendo, portanto, um dispositivo unipolar – trata-se do transistor de efeito

de campo (FET - de Field Effect Transistor), assim chamado porque o controle da corrente é realizado

pela ação de um campo elétrico convenientemente aplicado.

Tomando como base o conhecimento prévio sobre o transistor bipolar de junção, estudaremos as

características, a correta polarização e as aplicações mais relevantes para o transistor de efeito de campo.

Sempre que possível, será feita uma comparação entre esses dois tipos de transistores.

Em termos de história, a concepção dos transistores de efeito de campo é anterior à dos

transistores bipolares. As primeiras patentes relacionadas ao transistor de efeito de campo datam da

segunda e da terceira décadas do século XX, enquanto a patente do transistor bipolar é de 1948. No

entanto, a produção do transistor bipolar em escala industrial já era uma realidade em 1956, ao passo

que o transistor de efeito de campo só alcançou essa condição no início da década seguinte.

As particularidades desses dois dispositivos fazem com que um apresente vantagens e

desvantagens em relação ao outro, dependendo do tipo de aplicação. Esse fato justifica que ambos

continuem sendo produzidos. A Tabela 7-1 apresenta uma comparação entre eles.

TABELA 7-1 – COMPARAÇÃO ENTRE TRANSISTORES DE EFEITO DE CAMPO E TRANSISTORES BIPOLARES

A principal vantagem dos FETs é a maior escala de integração. Numa pastilha de circuito

integrado podem ser incluídos sete vezes mais transistores de efeito de campo do que bipolares. Isso

permite funções muito mais complexas para uma mesma área de chip. A maior desvantagem dos FETs é

seu menor produto ganho x banda passante (GBW), ou seja, um amplificador a FET terá, em geral, um

ganho menor do que um amplificador a transistor bipolar que tenha a mesma banda passante.

Transistor de Efeito de

Campo Transistor Bipolar

Máxima corrente menor maior

Frequência de corte menor maior

Linearidade menor maior

Ganho de tensão menor maior

Ganho de corrente maior menor

Impedância de entrada maior menor

Imunidade à radiação maior menor

Tolerância á temperatura maior menor

Escala de integração maior menor

Rapidez de chaveamento maior menor

Comportamento como chave normalmente fechado normalmente aberto

Mecanismo de controle corrente tensão

13

FAMÍLIAS DE TRANSISTORES DE EFEITO DE CAMPO

Existem duas principais famílias de transistores de efeito de campo: os transistores de efeito de

campo de junção (JFET – Junction Field Effect Transistor) e os transistores de efeito de campo de

porta isolada (IGFET - Insulated Gate Field Effect Transistor), mais conhecidos como transistores de

efeito de campo de metal-óxido-semicondutor (MOSFET – Metal-Oxide-Semiconductor Field Effect

Transistor). O desenvolvimento posterior levou ao surgimento de várias outras famílias, entre as quais

os transistores de efeito de campo de heterojunção (HFET – Heterojunction Field Effect Transistor),

os transistores de efeito de campo de metal-semicondutor (MESFET – Metal-Semiconductor Field

Effect Transistor) e os transistores de efeito de campo sensíveis a íons (ISFETs – Ion Sensitive Field

Effect Transistor). Nosso estudo abrangerá apenas as duas primeiras famílias.

TRANSISTOR DE EFEITO DE CAMPO DE JUNÇÃO - JFET

O JFET consiste basicamente numa barra semicondutora cuja condutância é controlada pela

aplicação de um campo elétrico perpendicular ao fluxo da corrente. Esse campo elétrico é resultante da

polarização reversa de uma junção PN que se forma na região intermediária da barra. Em cada uma das

extremidades são feitos contatos ôhmicos para a colocação de terminais, fazendo-se o mesmo na região

onde se formou a junção. A barra semicondutora recebe o nome de canal e a região de dopagem oposta

no meio do canal é chamada de porta ou gate (G), sendo a região de gate muito mais fortemente dopada

do que o canal.

A corrente no canal é composta exclusivamente de portadores majoritários. O terminal por onde

esses portadores entram no canal (a origem dos portadores) é chamado de fonte ou source (S) e o

terminal por onde eles saem do canal (o destino dos portadores) é chamado de dreno ou drain (D). Da

mesma forma que existem transistores bipolares dos tipos NPN e PNP, existem JFETs de canal N (cuja

corrente é constituída de elétrons livres) e de canal P (cuja corrente é constituída de lacunas).

Lembrando que os elétrons livres possuem maior mobilidade do que as lacunas, é muito mais frequente o

uso de JFETs de canal N do que de JFETs de canal P. A Figura 7-1 mostra o aspecto construtivo e a

simbologia dos JFETs canal N e canal P. Note-se que a diferenciação entre as simbologias é feita pelo

terminal de gate. Uma seta apontando para dentro do símbolo indica uma região com dopagem do tipo P.

Assim, um gate canal P significa que o canal é do tipo N. No caso do JFET canal P, a seta representativa

do gate aponta para fora, indicando uma região com dopagem do tipo N.

FIGURA 7-1 – ESTRUTURA INTERNA E SIMBOLOGIA DOS JFETS CANAL N E CANAL P

Source (S)

Dreno (D)

Gate (G)

Source (S)

Dreno (D)

Gate (G)

O desenho da estrutura permite observar que

o coletor de um transistor bipolar,

diferentes, mas se encontram em extremidades opostas de uma mesma região

caso se aplique uma tensão entre o dreno e o source, existe um caminho livre para a circulação da

corrente, não havendo nenhuma barreira representada por uma junção reversamente polarizada (como

ocorre quando se aplica uma tensão entre o coletor e o emissor de

Outro detalhe importante é que a região de gate se localiza mais pró

dreno. Esse fato é expresso na simbologia com a colocação da seta indicativa do gate mais próxima ao

terminal que representa o source. Deve

uma simbologia para o JFET em que a seta do gate se encontra exatamente no centro da distância entre o

dreno e o source. A forma mais segura de identificação dos terminais, portanto, é por meio da

configuração dos circuitos de polarização, que iremos abordar a seguir.

POLARI

A polarização de um JFET requer a aplicação de duas tensões: uma entre o gate e o source (VGS) e

outra entre o dreno e o source (VDS). A correta polarização de um JFET exige que a junção gate

seja reversamente polarizada. É dessa forma que se obtém a alta impedância de entrada do dispositivo.

Com relação à tensão entre dre

canal se desloquem do source para o dreno.

tensão VGS, considerando o source como o terminal de referência.

Tomando como exemplo um JFET de canal N (de uso mais frequente), o gate, que é do tipo P, deve

ter potencial negativo em relação ao source. Conseque

relação ao source. A Figura 7-2

FIGURA

Como visto anteriormente, na zona intermediária de uma junção PN existe uma região desprovida

de cargas móveis (e, assim, isolante), chamada de

reversamente polarizada, a largura

aplicada.

região de depleção

WCH

O desenho da estrutura permite observar que, ao contrário do que ocorre em relação ao emissor e

o coletor de um transistor bipolar, o dreno e o source de um JFET não se encontram em regiões

diferentes, mas se encontram em extremidades opostas de uma mesma região

caso se aplique uma tensão entre o dreno e o source, existe um caminho livre para a circulação da

corrente, não havendo nenhuma barreira representada por uma junção reversamente polarizada (como

quando se aplica uma tensão entre o coletor e o emissor de um transistor bipolar).

Outro detalhe importante é que a região de gate se localiza mais pró

dreno. Esse fato é expresso na simbologia com a colocação da seta indicativa do gate mais próxima ao

terminal que representa o source. Deve-se tomar cuidado, no entanto, porque muitos diagramas utilizam

JFET em que a seta do gate se encontra exatamente no centro da distância entre o

dreno e o source. A forma mais segura de identificação dos terminais, portanto, é por meio da

configuração dos circuitos de polarização, que iremos abordar a seguir.

POLARIZAÇÃO E PRINCÍPIO DE OPERAÇÃO DO JFET

polarização de um JFET requer a aplicação de duas tensões: uma entre o gate e o source (VGS) e

outra entre o dreno e o source (VDS). A correta polarização de um JFET exige que a junção gate

polarizada. É dessa forma que se obtém a alta impedância de entrada do dispositivo.

Com relação à tensão entre dreno e source, ela deve ter polaridade tal que os portadores majoritários do

canal se desloquem do source para o dreno. Para tanto, a polaridade da tensão VDS deve ser

tensão VGS, considerando o source como o terminal de referência.

Tomando como exemplo um JFET de canal N (de uso mais frequente), o gate, que é do tipo P, deve

ter potencial negativo em relação ao source. Consequentemente, o dreno deve ter potencial negativo em

2 ilustra a correta polarização de um JFET canal N.

FIGURA 7-2 – POLARIZAÇÃO DE UM JFET CANAL N

Como visto anteriormente, na zona intermediária de uma junção PN existe uma região desprovida

de cargas móveis (e, assim, isolante), chamada de região de depleção. No caso de uma junção

polarizada, a largura da região de depleção será proporcional ao módulo da tensão

região de depleção

VGS

14

, ao contrário do que ocorre em relação ao emissor e

dreno e o source de um JFET não se encontram em regiões

diferentes, mas se encontram em extremidades opostas de uma mesma região (no caso, o canal). Assim,

caso se aplique uma tensão entre o dreno e o source, existe um caminho livre para a circulação da

corrente, não havendo nenhuma barreira representada por uma junção reversamente polarizada (como

um transistor bipolar).

Outro detalhe importante é que a região de gate se localiza mais próxima ao source do que ao

dreno. Esse fato é expresso na simbologia com a colocação da seta indicativa do gate mais próxima ao

se tomar cuidado, no entanto, porque muitos diagramas utilizam

JFET em que a seta do gate se encontra exatamente no centro da distância entre o

dreno e o source. A forma mais segura de identificação dos terminais, portanto, é por meio da

OPERAÇÃO DO JFET

polarização de um JFET requer a aplicação de duas tensões: uma entre o gate e o source (VGS) e

outra entre o dreno e o source (VDS). A correta polarização de um JFET exige que a junção gate-source

polarizada. É dessa forma que se obtém a alta impedância de entrada do dispositivo.

deve ter polaridade tal que os portadores majoritários do

idade da tensão VDS deve ser oposta à da

Tomando como exemplo um JFET de canal N (de uso mais frequente), o gate, que é do tipo P, deve

ntemente, o dreno deve ter potencial negativo em

ilustra a correta polarização de um JFET canal N.

Como visto anteriormente, na zona intermediária de uma junção PN existe uma região desprovida

. No caso de uma junção

cional ao módulo da tensão

VDS

15

Suponhamos inicialmente que a tensão VGS esteja ajustada em zero (curto-circuito entre gate e

source). Com a aplicação da tensão VDS entre dreno e source, os portadores majoritários do canal

(elétrons livres, no caso de um JFET canal N) passam a fluir através do mesmo, estabelecendo-se a

corrente de dreno ID. A Figura 7-3 ilustra essa situação e mostra o comportamento da corrente de dreno

em função da tensão entre dreno e source.

FIGURA 7-3 – CORRENTE DE DRENO DE UM JFET EM FUNÇÃO DA TENSÃO ENTRE DRENO E SOURCE

Um fato importante a observar é que a tensão VDS também contribui para a polarização reversa

da junção porta-canal. Como o canal é N e possui potencial positivo, enquanto a tensão do gate é zero, a

junção está, de fato, reversamente polarizada. A tensão VDS se distribui linearmente ao longo do

comprimento l do canal. Logo, quanto mais próximo ao dreno, maior será a polarização reversa. Como a

largura da região de depleção é proporcional ao valor da tensão reversa, isso explica porque o canal é

mais estreito nas proximidades do dreno do que nas proximidades do source.

Para pequenos valores de VDS, a região de depleção entre o gate e o canal se mantém

relativamente estreita, e seu efeito sobre a corrente de dreno é desprezível, existindo, portanto, uma

relação linear entre a corrente de dreno e a tensão VDS. Esse é o comportamento na primeira parte da

curva característica, que compreende a região de operação chamada de linear, resistiva ou de triodo.

À medida que a tensão VDS aumenta, a região de depleção avança para o interior do canal,

reduzindo sua largura efetiva. Dessa forma, diminui a variação de corrente devida a uma dada variação

de tensão, isto é, a inclinação da curva, vai diminuindo, até que chega o ponto em que o aumento da

tensão VDS acarreta um aumento na mesma proporção na resistência do canal. A esse fenômeno dá-se o

nome de pinçamento, estrangulamento, constrição ou pinch-off. Como é possível observar através

do gráfico, após o estrangulamento a corrente de dreno varia muito pouco com o aumento da tensão

entre dreno e source, o que caracteriza uma saturação do valor da corrente de dreno. Esse valor

estabilizado de corrente, obtido com VGS = 0 é chamado de máxima corrente de saturação de dreno

(IDss).

Note-se que não é possível fechar totalmente o canal apenas aumentando-se o valor de VDS. Com

o canal totalmente fechado, não circularia corrente por ele e a distribuição de tensão que causou o

pinçamento não mais existiria. Pelas razões expostas acima, essa região de operação do JFET é chamada

de região de pinch-off, de corrente constante ou de saturação. O valor de tensão entre dreno e source

que leva ao pinçamento de canal é chamado de tensão de pinçamento ou tensão de pinch-off (VP).

IDss e VP são os dois parâmetros mais importantes de um JFET.

RD

VDD avalanche

16

Aumentando-se ainda mais a tensão entre dreno e source, a junção porta-canal entra na região de

avalanche, na qual a corrente cresce indefinidamente, podendo danificar o dispositivo caso não existam

elementos limitadores. Trata-se de um processo análogo ao que ocorre nos diodos Zener. A tensão

entre dreno e source que leva o JFET a entrar na região de avalanche é outro parâmetro importante de

um JFET. Esse parâmetro é denominado como BVDSS ou B(VR)DSS nos manuais e folhas de dados, e é

da ordem de algumas dezenas de volts. O projetista de circuitos utilizando JFET deve garantir que este

não entre na região de avalanche.

Utilizando agora uma tensão VGS entre gate e source diferente de zero, essa se soma à tensão VDS

na polarização reversa da junção gate-canal. Com isso, o valor da corrente de dreno será, para cada valor

de VDS, menor do que no caso anterior (em que VGS = 0). Como a junção porta-canal está reversamente

polarizada, a corrente de gate IG é praticamente nula (da ordem de nA), resultando numa impedância de

entrada muito alta para o JFET. Assim, o controle da corrente de dreno é feito basicamente pelo campo

elétrico gerado pela tensão VGS.

Quanto maior (em módulo), o valor da tensão VGS, menor será a largura efetiva do canal, até

chegar ao ponto de seu total fechamento, quando a corrente de dreno terá valor essencialmente nulo. Na

prática, nessas condições circula uma corrente da ordem de nA, chamada de IDoff. Outra forma de definir

a tensão de pinch-off VP é como a tensão entre gate e source que causa o fechamento completo do canal.

Por esse motivo, a tensão de pinch-off é simbolizada também como VGS(off). Quanto maior o módulo da

tensão VGS, menor o valor necessário da tensão VDS para que o JFET atinja a região de avalanche.

A Figura 7-4 mostra o comportamento do JFET para uma tensão VGS diferente de zero e um

gráfico com valores típicos para as curvas características do dispositivo, mostrando claramente as três

regiões de operação.

FIGURA 7-4 – COMPORTAMENTO DO JFET PARA TENSÕES VGS DIFERENTES DE ZERO

O gráfico das curvas características permite observar uma diferença essencial entre o JFET e o

transistor bipolar. Enquanto num transistor bipolar a região de operação depende basicamente da

forma como são polarizadas as duas junções, num JFET a região de operação depende basicamente do

valor da tensão VDS entre dreno e source, sem qualquer alteração na polaridade das tensões de

polarização (VDS e VGS).

A região de depleção se alarga com o aumento de VGS, até o fechamento total do canal, cessando o fluxo da corrente de dreno ID.

linear pinchoff avalanche

17

Para pequenos valores de VDS, o JFET está na região resistiva. Quando a tensão entre dreno e

source aumenta até causar o estrangulamento do canal, o JFET passa para a região de corrente constante,

na qual permanece até que VDS ultrapassa o valor necessário para causar a avalanche da junção gate-

canal. Considerando-se a ação combinada das tensões VDS e VGS (ambas tomadas em módulo, já que

têm polaridades opostas), a região de operação em que um JFET se encontra pode ser determinada pela

seguinte regra:

Para VDS ≤ VP@VGSLL

MM, o JFET se encontra na região linear ou resistiva;

Para VP@VGSLL

MM< VDS ≤ BDVSS@VGS

LL

MM, o JFET se encontra na região de pinch-off ou de

corrente constante;

Para VDS > BDVSS@VGSLL

MM, o JFET se encontra na região de avalanche (o que deve ser evitado).

A Figura 7-5 mostra em detalhes a fronteira entre as regiões resistiva e de corrente constante de

um JFET canal N que possui VP = -3,6 V e IDss = 9 mA. A figura não inclui a região de avalanche.

FIGURA 7-5 – DETALHAMENTO DO LIMITE ENTRE AS REGIÕES LINEAR E DE PINCH-OFF DE UM JFET

EXEMPLO 7-1: UM JFET POSSUI TENSÃO DE PINCH-OFF IGUAL A 3 V E TENSÃO DE AVALANCHE IGUAL A 35 V. EM

QUE REGIÃO ESSE JFET ESTARÁ OPERANDO CASO O GATE E O SOURCE ESTEJAM EM CURTO E A SUA TENSÃO

ENTRE DRENO E SOURCE VALHA:

A) 30 V. B) 2,5 V. C) 5 V. D) 40 V. E) 10 V.

VGS = -3,0 V

VGS = -2,4 V

VGS = -1,8 V

VGS = -1,2 V

VGS = -0,6 V

VGS = 0,0 V

região de corrente constante (VDS > VP – VGS)

Linha indicativa de VDS = VP – VGS

região resistiva (VDS ≤≤≤≤ VP – VGS)

1,2 2,4 3,6 4,8 6,0 7,2 8,4 VDS (V) (VP) VGS ≤≤≤≤ -3,6 V (ID ≈ 0)

ID (mA)

9 (IDss)

8

7

6

5

4

3

2

1

0

18

O JFET OPERANDO NA REGIÃO LINEAR OU RESISTIVA

Na parte inicial das curvas características de um JFET a tensão VDS tem influência desprezível na

polarização reversa da junção. Desse modo, a resistência do canal dependerá apenas do valor da tensão

aplicada entre gate e source, e a corrente variará linearmente em função da tensão VDS entre dreno e

source. Nessas condições, o canal pode ser considerado como um resistor cuja resistência depende de

VGS (quanto maior VGS, maior será a resistência do canal) e é chamada de RDSon. O menor valor

possível para RDSon é chamado de Ro e será obtido, obviamente, quando a tensão entre gate e source for

igual a zero. Os JFETs comerciais possuem valor de Ro situado entre 10 Ω e 100 KΩ.

A Figura 7-6 mostra uma ampliação da parte inicial (VDS na ordem de centenas de milivolts) da

região resistiva para um JFET canal N.

FIGURA 7-6 – DETALHAMENTO DA REGIÃO LINEAR DE OPERAÇÃO DE UM JFET CANAL N

A figura permite visualizar claramente as diferentes inclinações da curva, em função da tensão

entre gate e source. Cada inclinação corresponde a um diferente valor de resistência de canal RDSon. É

possível calcular o valor da resistência de canal através da equação:

RDSON =Ro

1@ VGS

VPffffffffffffffffff

ffffffffffffffffffffffff (EQUAÇÃO 7-1).

É evidente que para valores de VGS com módulo igual ou superior a VP, o canal estará totalmente

fechado e a sua resistência será “infinita”. A equação nos mostra que a resistência do canal pode ser

variada através da tensão entre gate e source, ou seja, trata-se de uma resistência controlada por

tensão , também conhecida como VDR (Voltage Dependant Resistance).

Como se pode ver, as curvas passam pela origem (VDS = 0 e ID = 0). Isso significa que o JFET não

possui offset, ou seja, não exige uma tensão mínima para iniciar a condução (como é o caso de um diodo

ou de um transistor bipolar). Isso é bastante vantajoso em várias aplicações.

Outra característica que pode ser notada é que na região linear as curvas são praticamente

simétricas em relação à origem, o que indica que a polaridade de VDS pode ser invertida sem que as

características de funcionamento se alterem de modo significativo.

19

EXEMPLO 7-2: O JFET UTILIZADO NO CIRCUITO ABAIXO POSSUI TENSÃO DE PINCH-OFF IGUAL A -2 V E MÁXIMA

CORRENTE DE SATURAÇÃO DE DRENO IGUAL A 6 mA. SABENDO QUE O VALOR DA CORRENTE DE DRENO É 4 mA:

A) CALCULAR O VALOR DA TENSÃO VO CASO A TENSÃO ENTRE GATE E SOURCE SEJA AJUSTADA PARA -1 V.

B) CALCULAR O VALOR DA TENSÃO ENTRE GATE E SOURCE PARA QUE A CORRENTE PASSE PARA 2 mA.

A fórmula genérica que permite o cálculo da corrente de dreno de um JFET operando na região

resistiva em função dos seus parâmetros e das tensões de polarização é:

ID =IDssBVDS

VP2

ffffffffffffffffffffffffffffffffffB 2B VP@VGS

` a@VDS

B C

(EQUAÇÃO 7-2).

Ao se utilizar a equação acima é importante ter em mente que sua validade se limita à região

resistiva de operação (quando VDS ≤ VP@VGSLL

MM) e que todas as tensões envolvidas na equação devem ser

consideradas em módulo. Outro ponto importante é que o dispositivo só obedecerá à equação caso as

condições de polarização (valor da tensão de alimentação e dos resistores associados) assim o

permitirem.

EXEMPLO 7-3: PARA O CIRCUITO DO EXEMPLO 7-2, CALCULAR O VALOR NECESSÁRIO DA TENSÃO DE

ALIMENTAÇÃO PARA QUE A CORRENTE DE DRENO DO JFET CHEGUE A IDss, SEM QUE O MESMO SAIA DA REGIÃO

RESISTIVA.

RD 1 KΩ

VDD 5 V

20

APLICAÇÕES DO JFET NA REGIÃO LINEAR OU RESISTIVA

Como vimos, em sua operação na região linear a resistência de um JFET é controlada pela tensão

aplicada entre gate e source. Esse comportamento proporciona algumas aplicações para o dispositivo,

que veremos a seguir.

CIRCUITOS DE CONTROLE AUTOMÁTICO DE GANHO PARA AMPLIFICADORES

Em algumas situações é importante que se controle o ganho de um amplificador de modo a evitar

alterações bruscas no comportamento quando o sinal de entrada varia subitamente. Um exemplo dessa

situação é quando, numa emissora de TV, o volume aumenta significativamente durante os intervalos

comerciais (prática proibida pela legislação, mas muito utilizada).

Um circuito de controle automático de ganho (AGC – Automatic Gain Control) diminui o ganho do

amplificador quando a intensidade do sinal de entrada aumenta e aumenta o ganho quando a intensiade

do sinal de entrada diminui, mantendo dessa forma o nível do sinal de saída. O diagrama em blocos de

um circuito típico de AGC utilizando JFET é mostrado na Figura 7-7.

FIGURA 7-7 - JFET UTILIZADO EM CONTROLE AUTOMÁTICO DE GANHO

Como sabemos, o módulo do ganho de tensão de um amplificador transistorizado emissor comum

sem capacitância de desvio no emissor é dado, aproximadamente, pela equação: AvLL

MMt

RC

REffffffffffff. No caso do

diagrama da Figura 7-7, a resistência de emissor é dada pela associação paralela entre o resistor RE e a

resistência de canal RDSon do JFET, de maneira que o módulo do ganho de tensão deste circuito

específico será: AvLL

MMt

RCREBRDSon

RE + RDSonffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffffff. O JFET não influi sobre a polarização DC do amplificador

transistorizado devido à presença do capacitor de desacoplamento CAGC., que faz com que a resistência de

canal só tenha influência sobre o sinal alternado a ser amplificado.

Se, por qualquer razão, o ganho do amplificador aumenta, o valor do sinal de saída vo também

aumenta, bem como o nível DC na saída do filtro. Se o sinal de saída do filtro polariza reversamente a

junção porta-canal, um aumento nessa tensão acarreta um aumento de RDSon, o que, por sua vez, reduz o

valor do ganho.

21

As relações de causa e efeito são: Av ↑↑↑↑ ⇒⇒⇒⇒ vo ↑↑↑↑ ⇒⇒⇒⇒ VGS ↑↑↑↑ ⇒⇒⇒⇒ RDSon ↑↑↑↑ ⇒⇒⇒⇒ Av ↓↓↓↓. Logo, um

aumento do ganho acaba acarretando sua própria diminuição, ou seja, o AGC introduz um efeito

estabilizador sobre o ganho do amplificador. Usando um raciocínio análogo, constata-se que uma

eventual diminuição do ganho também será compensada por esse circuito.

O JFET COMO DISPOSITIVO DE CHAVEAMENTO

Da mesma forma como o transistor bipolar, o JFET também pode ser empregado como dispositivo

de chaveamento, que é uma aplicação binária, ou seja, que envolve dois estados. Para tanto, a tensão de

gate deve ser de tal forma que faça o JFET transitar da condução plena (|VGS| ≈ 0, levando o JFET a se

comportar como uma chave fechada) para a condição de canal fechado (|VGS| ≥≥≥≥ |VP|, levando o JFET a se

comportar como uma chave aberta).

O desempenho do JFET como chave é um pouco inferior ao de um transistor bipolar, pois quando

ligado (|VGS| ≈ 0), a resistência RDSon não é nula, mas possui um valor da ordem de dezenas ou até

mesmo centenas de Ω. Quando desligado |VGS| ≥≥≥≥ |VP|), a resistência do canal é praticamente infinita, e o

comportamento é semelhante ao de uma chave aberta. Com isso em mente, é fácil compreender o

funcionamento de um circuito de chaveamento com JFET, como o mostrado na Figura 7-8.

FIGURA 7-8 - CIRCUITO BÁSICO DE CHAVEAMENTO COM JFET E RESPECTIVAS FORMAS DE ONDA

A tensão de controle vCONTROL, aplicada ao gate do JFET, é um sinal binário. Um dos seus valores

(nível “1”) deve ser levemente positivo e o outro (nível “0”) deve ser mais negativo do que a tensão de

pinch-off. Assim, quando o sinal de controle estiver em nível “1” a resistência entre dreno e source será

mínima e o valor da tensão de saída será:

vo = vRL =viBRL

RDSON + RLfffffffffffffffffffffffffffffffffff

(EQUAÇÃO 7-3).

Logo, para que o circuito seja eficiente, é necessário que RL >> RDSON. Isso garante que a tensão

sobre RL seja praticamente igual à tensão de entrada e também que a tensão entre dreno e source VDS

seja próxima de zero, o que é essencial para que o JFET apresente um comportamento resistivo (se VDS

>> 0, o JFET entra na região de saturação).

22

Quando o sinal de controle estiver em nível “0”, o canal do JFET estará “fechado”, resultando numa

corrente e numa tensão de saída praticamente nulas.

O gráfico da Figura 7-8 mostra como exemplo uma tensão de entrada vi constante, representada

pela reta pontilhada. Na prática, esse sinal pode ter qualquer forma de onda, inclusive alternada, visto

que na região resistiva o comportamento do JFET é praticamente simétrico, ou seja, funciona

corretamente para qualquer polaridade da tensão VDS. As únicas precauções a serem tomadas dizem

respeito aos limites de corrente e de frequência de operação.

O circuito da Figura 7-8 mostra o JFET como uma chave colocada em série com a carga. Ele pode

ser também colocado em paralelo, como mostra o diagrama da Figura 7-9.

FIGURA 7-9 – JFET COMO CHAVE EM PARALELO

Para este circuito, quando a tensão de controle estiver em nível “0”, a tensão VGS do JFET será

nula e a resistência de canal terá o seu valor mínimo. Supondo que não exista resistência de carga

conectada, a tensão de saída vo valerá:

vo = vRDSON=

viBRDSON

RDSON + RDfffffffffffffffffffffffffffffffffff

(EQUAÇÃO 7-4).

Sendo RD >> RDSON, a tensão de saída nessa situação será praticamente zero. Caso a tensão de

controle esteja em nível “1” (tensão negativa com módulo igual ou superior a VP), o canal do JFET estará

completamente fechado, não circulará corrente pelo circuito e teremos: vo = vi. Caso seja conectada

uma resistência de carga RL aos terminais de saída, é necessário que RL >> RD, par um bom desempenho

do circuito.

Uma variação interessante da aplicação do JFET como dispositivo de chaveamento é como

multiplexador analógico, conforme mostrado no diagrama da Figura 7-10.

FIGURA 7-10 – DIAGRAMA BÁSICO DE MULTIPLEXADOR ANALÓGICO UTILIZANDO JFET

RD

D

R G

vi vo

vCONTROL

R L

R L

vi1

vi2

vi3

vc1 vc2 vc3

vo

23

O princípio de funcionamento é bastante simples. Supondo que todos os sinais de controle (vc1,

vc2 e vc3) estejam em nível “1” (tensão negativa com módulo igual ou superior a VP), todos os JFETs

estarão cortados e o sinal de saída será nulo. Se uma das tensões de controle for para nível “0”, o JFET

correspondente entra em condução plena e o sinal de saída será aproximadamente igual ao sinal de

entrada aplicado ao source do JFET em questão (observadas as condições comentadas acima). Em geral,

apenas uma das entradas de controle deverá estar em nível “0” num determinado instante. Se houver

mais de uma entrada em nível “0”, o circuito passa a funcionar como misturador de sinais, e não

apresenta um bom desempenho.

Uma última observação é que as análises e descrições acima se referem a JFETs de canal N. Para

JFETs de canal P, a polaridade da tensão de controle tem que ser invertida.

O JFET OPERANDO NA REGIÃO DE PINCH-OFF

Conforme vimos anteriormente, à medida que a tensão entre o dreno e o source aumenta, dois

processos conflitantes passam a ocorrer: com o aumento da tensão VDS, a corrente de dreno tenderia a

aumentar, mas, simultaneamente, a redução da largura do canal aumenta a resistência dessa região, o que

tenderia a diminuir a corrente de dreno. A soma desses dois efeitos leva a uma estabilização do valor da

corrente de dreno - é a chamada corrente de saturação de dreno (IDs). Isso explica a pequena variação

da corrente de dreno em relação à variação de VDS que ocorre na região de pinch-off, como observado no

gráfico da Figura 7-4.

O mesmo gráfico permite constatar que valor da corrente de saturação será dependente da tensão

entre gate e source (VGS). O maior valor para essa corrente será atingido, evidentemente, quando VGS for

igual a zero. Esse valor máximo da corrente de saturação de dreno é chamado de máxima corrente de

saturação de dreno (IDss). Conhecidos os valores de IDss e de VP, é possível calcular o valor da

corrente de saturação de dreno para valores de VGS diferentes de zero através da chamada Equação de

Shockley, que é válida somente quando o JFET se encontra na região de pinch-off:

IDs = IDssB 1@VGS

VPfffffffffffffff g2

(EQUAÇÃO 7-5).

Colocando a Equação 7.5 em forma gráfica, podemos traçar a curva de transferência do JFET

(também conhecida como curva de transcondutância), assim chamada porque relaciona uma grandeza

de saída (IDs) com uma grandeza de entrada (VGS). Essa curva é mostrada na Figura 7-11.

FIGURA 7-11 – CURVA DE TRANSFERÊNCIA DE UM JFET OPERANDO NA REGIÃO DE PINCH-OFF VGS

IDs IDss

VP

24

Como a Equação 7.5 permite deduzir, a curva mostrada no gráfico acima é uma parábola. Está

traçada no segundo quadrante apenas para deixar evidente que a polaridade da tensão entre gate e

source VGS é negativa em relação ao sentido da corrente de dreno IDs. A curva está limitada, na prática,

pelo eixo vertical, à direita, e pelo ponto VGS = VP, IDs = 0, à esquerda. Cruzar o eixo vertical significaria

uma inversão na polaridade da tensão VGS, o que não é permitido na operação de um JFET. Para valores

de VGS superiores (em módulo) a VP, o canal se fecha totalmente e a corrente de dreno cai a zero.

A essa altura, é conveniente enfatizar o significado dos vários termos ligados à corrente de dreno,

para evitar equívocos desnecessários:

ID → Trata-se de qualquer valor da corrente de dreno, em qualquer das regiões de operação de um JFET.

IDs → Trata-se da corrente de saturação de dreno, ou seja, o valor relativamente estabilizado que essa corrente atinge enquanto o JFET se encontra na região de pinch-off.

IDss → Trata-se do máximo valor possível para a corrente de saturação de dreno, que é obtido quando o JFET se encontra na região de pinch-off e está polarizado com VGS = 0.

Estudaremos a seguir os circuitos que permitem polarizar o JFET na região de operação desejada.

CIRCUITOS DE POLARIZAÇÃO PARA O JFET

O conceito de polarização de um JFET é análogo ao já estudado nos casos do diodo semicondutor e

do transistor bipolar. Basicamente trata-se de proporcionar os valores adequados para as tensões entre

dreno e source (VDS) e entre gate e source (VGS) para levar o dispositivo a operar com o valor desejado

de corrente de dreno. Como vimos, a tensão entre dreno e source também tem influência no valor da

corrente de dreno, e essa influência poderá ser grande (caso o JFET esteja na região de triodo) ou

pequena (caso o transistor esteja na região de pinch-off). Logo, assim como num transistor bipolar as

coordenadas do ponto de operação estática são (VCE, IC), num JFET essas coordenadas serão (VDS, ID).

Voltamos a ressaltar a diferença fundamental entre um JFET e um transistor bipolar no que se

refere à região de operação. Enquanto num transistor bipolar diferentes regiões de operação se

estabelecem com diferentes polaridades das tensões entre base e emissor e entre base e coletor, num

JFET as polaridades das tensões entre gate e source e entre dreno e source permanecem inalteradas,

independente da região de operação. O que muda é o valor da tensão entre dreno e source.

Como no caso dos transistores bipolares, as duas tensões (de dreno e de gate) devem

preferencialmente ser obtidas a partir de uma única fonte de alimentação, com o auxílio de resistores de

polarização convenientemente dispostos e dimensionados.

Por suas particularidades construtivas e de princípio de funcionamento, o JFET é bem menos

influenciado pela temperatura do que um transistor bipolar. Por outro lado, a variação dos parâmetros

para uma dada especificação de JFET tende a ser muito grande. Para exemplificar, um JFET canal N

BF245 tem máxima corrente de saturação de dreno variando entre 2 mA (valor mínimo para o tipo A) e

25 mA (valor máximo do tipo C), uma variação de doze vezes e meia. Com relação à tensão de pinch-off,

para esse mesmo JFET os valores vão de -0,25 V até -8 V, uma variação de 32 vezes.

Essa variação nos parâmetros pode ser vista na Figura 7-12, onde se mostram os limites para a