Zilog

-

Upload

lius-fontenelle-carneiro -

Category

Documents

-

view

816 -

download

4

description

Transcript of Zilog

Carlos Igor Ramos Bandeira – 276650Henrique Holanda – 279424

Pedro Lázaro – 276661Rafael Coelho Assunção – 232335

23/05/2008

O microprocessador EZ80190 realiza busca de instrução em ciclo único, tem um clock de até 50MHz e a CPU é de 8 bits. Pode servir páginas sobre uma rede TCP/IP.

Características principais: Multiplicador 16 x 16 bit e acumulador 40-bit com SRAM dual-

port de 1kb; Endereçamento linear de 16MB; Watch-dog timer; Controlador DMA de 2 canais; Interface universal ZILOG (I2C, SPI, UART) com gerador de

baud rate; 32 bits de General-purpose E/S; Voltagem de suprimento de 3V a -3,6V com tolerância na

entrada de 5V; 100 pinos; Temperatura de operação: Normal – 0ºC a 70ºC Extendida – -40ºC a 105ºC

O ez80190 possui 6 PRT; Podem operar nos modos SINGLE PASS e

CONTINOUS MODE; Cada timer pode ser programado para:

Começar; Parar; Recomeçar de onde parou; Recomeçar do valor inicial da contagem; Gerar interrupçao.

Modo SINGLE PASS:

Quando o timer atinge o valor final da contagem,

ele é desabilitado;

Modo CONTINOUS MODE:

Quando o timer atinge o valor final da contagem,

ele automaticamente recarrega o valor inicial doTMRx_RR_H e TMRx_RR_L.

Registros: TIMERx Control Register (R/W) TIMERx Reload Low Byte Register (W) TIMERx Reload High Byte Register (W) TIMERx Data Low Byte Register (R) TIMERx Data High Byte Register (R)

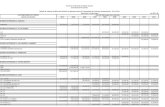

TIMER Control Registers:

TIMER Control Registers:

TIMER Data Low Byte Register: A leitura desse registro retorna o byte menos significativo

da contagem atual do timer

TIMER Data High Byte Register: A leitura desse registro retorna o byte mais significativo

da contagem atual do timer

TIMER Reload Low Byte Register: Esse registro guarda o byte menos significativo do

valor de recarga do timer.

TIMER Reload High Byte Register: Esse registro guarda o byte mais significativo do valor

de recarga do timer.

O dispositivo ez80190 inclui um WTD cujas características são:

Quatro programáveis períodos de intervalo de parada: 218, 222, 225 e 227;

Uma bandeira do indicador do reset do intervalo de parada de WDT;

Uma selecionável resposta de intervalo de parada: um intervalo de parada gera um reset ou um interrupção não mascarada.

Diagrama de blocos

Operação Habilitando e desabilitando o WDT; Seleção do período do intervalo de parada; Geração do RESET ou NMI.

Registros Registro de Controle; Registro de Reset.

O ez80190 possui 32bits de GPIO divididos em 4

portas de 8 bits cada; Cada porta possui quatro registros de 8bits; De acordo com os valores de cada bit dos registros,

cada bit de uma porta pode trabalhar em um modo; Existem 9 modos de operação.

Registros: Port x Data Register (Px_DR) Port x Data Direction Register (Px_DDR) Port x Alternate Register 1 (Px_ALT1) Port x Alternate Register 2 (Px_ALT2)

Modos de operação

DESCRIÇÃO FUNCIONAL

• 5 a 8 bits transmissão/recepção

• Start bit (geração e detecção)

• Paridade (geração e detecção)

• Stop bit (geração e detecção)

• Break (geração e detecção)

FUNÇÕES DA UART• O transmissor • O receptor • A interface com Modem

INTERRUPÇÕES• Transmissor • Receptor (3 interrupções diferentes ) • Modem status

RECOMENDAÇÃO DE USO DA UART • Módulo reset • Controlar transferências ao configurar a operação UART • Transferir dados

DESCRIÇÃO FUNCIONAL

RECOMENDAÇÃO DE USO DO GERADOR DE BAUD RATE• RESET • Setar UARTx_LCTL[7] para 1 para habilitar o acesso aos registros divisores do BRG. • Programar os registros BRGx_DLR_L e BRGx_DLR_H. • Resetar UARTx_LCTL[7] para 0 para desabilitar accesso aos registros divisores do BRG.

• Master In Slave Out (MISO)

• Master Out Slave In (MOSI)

• Slave Select (SS)

• Serial Clock (SCK)

• Descrição Funcional:

Características: 2 acumuladores de 40-bit; 1 multiplicador 16-bit x 16-bit com produto

de 32-bit; Cada operação MACC é completada em um

ciclo de clock; 2 espaços dual-port de RAM 256 x 16,

chamados de x e y; Registros de controle no espaço de E/S para

setar a próxima operação de MACC, iniciar a operação, determinar quando MACC completa o cálculo e devolver o resultado.

Processo mais significativo no processamento digital de sinais, baseado em somas de produtos

Operação recomendada: Carrega os dados nos espaços x e y da RAM; Lê status. Se DATA está EMPTY ou DONE um novo cálculo

pode ser escrito no registro do banco de dados; Usa instrução OTI2R para carregar novo cálculo; Se MACC está pronto os bancos DATA e CAL são trocados. A

equação que estava em DATA vai para CALC. O banco CALC muda para IN PROGRESS;

Lê status. Se MACC não concluiu espera. Quando terminar o cálculo, CALC muda para DONE;

Se DATA está EMPTY e CALC DONE, escreve 80h no registro de estatus. Os bancos são trocados e DATA muda para DONE;

A CPU lê o acumulador e pode reaver o resultado. DATA muda para EMPTY, a menos que haja outro resultado a reaver.

O microprocessador EZ80190 tem uma RAM de 1kb no Multiplicador-Acumulador. O MACC x DATA fica no endereço destinado aos 512 bytes inferiores e o MACC y DATA no endereço destinado aos 512 bytes superiores

MACC_x(y)START: define o endereço do primeiro valor de x e y

MACC_x(y)END: define o final do endereço linear para x e y.

MACC_x(y)RELOAD: define o endereço circular para ser usado quando o indice do contador x e y alcança o valor final para o espaço de endereço linear

MACC_LENGTH: define o tamanho do dado (quantos endereços serão usados)

Programação Modos de Transferência

Modo Burst; Modo Cycle-Steal.

Prioridades do Canal Interrupções Registros de Controle

São acessados pela CPU usando instruções de E/S.

Registros de Endereço da fonte do DMA

Registros de Endereço do destino do DMA

Registros da contagem de byte do DMA

Registros de Controle

[1] ez80190 ProductSpecification, disponível em:

Site: http://www.zilog.com

Acessado em 09/05/2008