Solución - ceictecunac.files.wordpress.com · Fig. 1 (Diseño del circuito en PROTEUS) ... de 4 a...

-

Upload

truonglien -

Category

Documents

-

view

241 -

download

3

Transcript of Solución - ceictecunac.files.wordpress.com · Fig. 1 (Diseño del circuito en PROTEUS) ... de 4 a...

1

D2

Q5

CLK3

Q6

S4

R1

U1:A

7474

D12

Q9

CLK11

Q8

S10

R13

U1:B

7474

D2

Q5

CLK3

Q6

S4

R1

U2:A

7474

D12

Q9

CLK11

Q8

S10

R13

U2:B

7474

D1

LED-YELLOW

D2

LED-YELLOWD3

LED-YELLOWD4

LED-YELLOW

1X

06

1Y

7

1X

15

1X

24

1X

33

2X

010

2Y

9

2X

111

2X

212

2X

313

A14

B2

1E

1

2E

15

U374153

1X

06

1Y

7

1X

15

1X

24

1X

33

2X

010

2Y

9

2X

111

2X

212

2X

313

A14

B2

1E

1

2E

15

U474153

0

0

1 1 0 0

1.-

Solución:

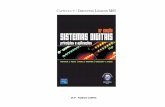

Fig. 1 (Diseño del circuito en PROTEUS)

En el circuito diseñado por el programa Proteus conectamos los LOGISCTATE a los

multiplexores TLL 74LS153 y de la salida del integrado conectamos a los FF-D

74LS74 Síncrono.

Este dispositivo que vemos en la figura 1 es un sistema secuencial que maneja los

datos de cada entrada del selector hacia el flip flop D y esta con el CLOCK (funciona

tipo timer monoestable) en conjunto explusa mediante la señal de control AB.

CONTROL A B

DERECHA 0 1

IZQUIERDA 1 0

2

2.-

Solución:

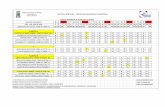

Tabla de circuito de control

AE AS1 AS0 BE ES1 ES0 CE CS1 CS0 DE DS1 DS0 FUNCION

1 0 0 0 0 0 0 0 0 0 0 0 Datos de

AA

1 0 1 0 0 0 0 0 0 0 0 0 Datos de

BA

1 1 0 0 0 0 0 0 0 0 0 0 Datos de

CA

1 1 1 0 0 0 0 0 0 0 0 0 Datos de

DA

0 0 0 1 0 0 0 0 0 0 0 0 Datos de

AB

0 0 0 1 0 1 0 0 0 0 0 0 Datos de

BB

0 0 0 1 1 0 0 0 0 0 0 0 Datos de

CB

0 0 0 1 1 1 0 0 0 0 0 0 Datos de

DB

0 0 0 0 0 0 1 0 0 0 0 0 Datos de

AC

0 0 0 0 0 0 1 0 1 0 0 0 Datos de

BC

0 0 0 0 0 0 1 1 0 0 0 0 Datos de

CC

0 0 0 0 0 0 1 1 1 0 0 0 Datos de

DC

0 0 0 0 0 0 0 0 0 1 0 0 Datos de

DA

0 0 0 0 0 0 0 0 0 1 0 1 Datos de

DB

3

0 0 0 0 0 0 0 0 0 1 1 0 Datos de

DC

0 0 0 0 0 0 0 0 0 1 1 1 Datos de

DD

A B

CD

74LS194CP

S1S0

DSRDSL

MR

D3D2D1D0

Q3Q2Q1Q0

U12

+V

V165V

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U11

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U10

74LS194CP

S1S0

DSRDSL

MR

D3D2D1D0

Q3Q2Q1Q0

U9

+V

V125V

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U8

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U7

74LS194CP

S1S0

DSRDSL

MR

D3D2D1D0

Q3Q2Q1Q0

U5

+V

V65V

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U3

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U2

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U4

74LS153I3aI2aI1aI0aS1S0

I3bI2bI1bI0b

Ea

Eb

Ya

Yb

U6

+V

V55V

74LS194CP

S1S0

DSRDSL

MR

D3D2D1D0

Q3Q2Q1Q0

U1

161284

151173

141062

13951

1

16151413

1

161284

151173

141062

13951

1

1211109

1

161284

151173

141062

13951

1

8765

1

161284

151173

141062

13951

1

4321

1

1

1

1

1

1

1

1

1

Fig. 2 (Diseño del circuito de registro en PROTEUS)

Funcionamiento:

En el circuito utilizamos un registro 74LS94, como podemos apreciar en el diseño del

circuito están configurado en forma paralela para la transferencia de datos entre (A

hacia A, A hacia B, A hacia C, A hacia D, B hacia A, etc.)

Para la transferencia de los datos utilizaremos un integrado multiplexor (seleccionador

de datos) de 4 a 1 (integrado 74LS153), el cual tiene una entrada de habilitación o de

enable.

Según como quiera realizar la trasferencia de datos a través de los registros se

configura la entrada del circuito de control que esta constituido por los multiplexores.

4

3.-

Solución:

Como observamos para el análisis del circuito dado debemos simular a través del

programa PROTEUS para ver el comportamiento del funcionamiento del FF-D.

1

2

3

U1:A

74LS32

4

5

6

U1:B

74LS32

D2

Q5

CLK3

Q6

S4

R1

U2:A

74LS74

0

R110k

C1

1u

A

B

C

D

Fig. 3 (circuito simulado en PROTEUS)

5

A) Diagrama de Tiempo

En el diagrama de tiempo analizamos con las entradas dadas X= 000101011 y Q = 0, la

salida “Z” del integrado 74LS32 por consiguiente graficamos su comportamiento con

respecto al tiempo.

Fig. 4(Diagrama de tiempo con respecto a la salida Z)

B) Diagrama de estados

C) Tabla de estado

X D nQ

nQ Z

0 1 0 1 0

0 0 1 0 1

0 1 0 1 0

1 1 1 0 1

6

J4

Q15

CLK1

K16

Q14

S2

R3

U1:A

7476

J9

Q11

CLK6

K12

Q10

S7

R8

U1:B

7476

J4

Q15

CLK1

K16

Q14

S2

R3

U2:A

7476

J9

Q11

CLK6

K12

Q10

S7

R8

U2:B

7476

1

2

3

U3:A

74LS32

12

3

U4:A74LS08

4

5

6

U3:B

74LS32

1

2

3

U5:A

74LS266

5 6

4

U5:B74LS266

9

10

8

U3:C

74LS32

4

5

6

U4:B

74LS08

9

10

8

U4:C

74LS08

8

9

10

U5:C

74LS266

1

2

3

U6:A

74LS86

12

13

11

U4:D

74LS08

12

13

11

U3:D74LS32

1

2

3

U7:A

74LS32

4 5

6

U7:B74LS32

1

2

3

U8:A

74LS08

4 5

6

U8:B74LS08

A7

QA13

B1

QB12

C2

QC11

D6

QD10

BI/RBO4

QE9

RBI5

QF15

LT3

QG14

U9

7447

U1:A(CLK)

1

JA

QB

QC Q

D

A

B

C

D

QA

QB

QC

QD

4.-

Solución:

Fig. 5(Diseño de un contador sincrono con Flip Flop JK)

7

A) Gráfica en función al tiempo de los estados de los estados de los flip flop J K.

CLOCK

JA

KA

JB

KB

CLOCK

JC

KC

JD

KD

B) La secuencia de números del circuito diseñado es: 0, 15, 10, 5, 13, 4, 11, 6, 1, 12 así

sucesivamente

QD QC QB QA

0 0 0 0

1 1 1 1

1 0 1 0

0 1 0 1

1 1 0 1

0 1 0 0

1 0 1 1

0 1 1 0

0 0 0 1

1 1 0 0

8

5.-

Tabla codificado en numero con signo en complemento a dos, desde +5, +4, +3, +2,

+1, 0 , -1, -2,-3, -4, -5, -6.

Nº A B C D

5

4

3

2

1

0

15

14

13

12

11

10

0 1 0 1

0 1 0 0

0 0 1 1

0 0 1 0

0 0 0 1

0 0 0 0

1 1 1 1

1 1 1 0

1 1 0 1

1 1 0 0

1 0 1 1

1 0 1 0

9

C110u

R1

220

1 2

3

U2:A74LS08

A7

QA13

B1

QB12

C2

QC11

D6

QD10

BI/RBO4

QE9

RBI5

QF15

LT3

QG14

U8

7447

1

D015

Q03

D11

Q12

D210

Q26

D39

Q37

UP5

TCU12

DN4

TCD13

PL11

MR14

U1

741930

2345

1

U9:A74HC4072

1 2

U3:A

74LS04

3 4

U3:B

74LS04

Funcionamiento:

Para que cuente desde +5, +4, +3, +2, +1, 0, 15, 14, 13, 12, 11, 10. Codificado en

número con signo en complemento a dos, debemos utilizar un integrado 74LS193 que

tiene la funciona UP/DOWN, en el circuito vemos que la entrada del integrado

74LS193 esta en 0101 y comienza en función de DOWN del 0101 hasta 0000 luego

cambia debido a que la salida del integrado esta conectado mediante un OR, este se

conecta mediante unas de las entrada del AND y la otra entrada esta conectado hacia

el reset out donde su salida va hacia la entrada del DOWN este circuito diseñado

hace que cuando llegue a 0000 el circuito haga reset y comience a contar en UP

desde 1111 hasta 1010. Cuando llegue a 1010 el circuito hace otra vez reset y cuenta

ahora en DOWN.

6.-

10

Solución:

El circuito funciona de la siguiente manera, cuando el primer CI 74193 llegue a 15

(1111) nos va a mandar una señal por medio de la compuerta nand de 4 entradas que

están conectadas a su salida del contador y esta a su vez a la compuerta or esta señal se

invierte y llega un pulso al flip flop JK y como el J y el K están conectados a “1” lógico

van a cambiar sus salidas del flip flop y esto va a ser que se vuelva el contador a down

gracias a las compuertas and ; y para que el contador no comience siempre de cero y

vaya aumentando progresivamente del numero que comienza se uso el segundo CI

74193 que cada vez que el primer contador llegue a 15 (1111) le van a mandar una

señal de clock y va a contar y las salidas de los 2 contadores se van a comparar y

cuando sean iguales se manda un pulso de clock al flip flop y este va a ser que el primer

contador cuente a partir del numero que aparece en el segundo contador y termine en

ese mismo número.

Fig. 6 (Diseño de un contador 74LS193 con Flip Flop D)

7.-

D015

Q03

D11

Q12

D210

Q26

D39

Q37

UP5

TCU12

DN4

TCD13

PL11

MR14

U1

74193

D015

Q03

D11

Q12

D210

Q26

D39

Q37

UP5

TCU12

DN4

TCD13

PL11

MR14

U2

74193

A010

A112

A213

A315

B09

B111

B214

B31

A<B2

QA<B7

A=B3

QA=B6

A>B4

QA>B5

U3

7485

1

2

3

U5:A

7408

4

5

6

U5:B

7408

D2

Q5

CLK3

Q6

S4

R1

U4:A

7474

12

U6:A7404

1

2

3

U7:A

7432

D12

Q9

CLK11

Q8

S10

R13

U4:B

7474

9

10

8

U5:C

7408

D1

LED-YELLOW

D2

LED-YELLOW

D3

LED-YELLOW

D4

LED-YELLOW

11

A) Mapa de transición de Estado

δ (00 , S0 ) = S0

δ (01 , S0 ) = S0

δ (10 , S0 ) = S1

δ (00 , S1) = S0

δ (10 , S1 ) = S1

δ (11 , S1 ) = S2

δ (01 , S2 ) = S3

δ (10 , S2 ) = S3

δ (11 , S2 ) = S2

δ (00 , S3 ) = S0

δ (01 , S3 ) = S3

δ (10 , S3 ) = S3

δ (11 , S3 ) = S3

B) Mapa de Funcion de Salida

(00 , S0 ) = 0

(01 , S0 ) = 0

(10 , S0 ) = 0

(00 , S1 ) = 0

(10 , S1 ) = 0

(11 , S1) = 0

(01 , S2 ) = 0

(10 , S2 ) = 1

(11 , S2) = 0

(00 , S3 ) = 0

(01 , S3 ) = 0

(10 , S3 ) = 1

(11 , S3 ) = 0

C) Tabla de Estados

Estados Entradas

00 01 10 11

S0 S0/0 S0/0 S1/0 x/x

S1 S0/0 x/x S1/0 S2/0

S2 x/x S3/0 S3/1 S2/0

S3 S0/0 S3/0 S3/1 S3/0

D) Para el diseño del FF-JK:

Los Estados { 3S , 2S , 1S , 0S }={11,10,01,00}

Las entradas { 12 , XX }= {00,01,10,11}

Se utiliza 2 FF-JK

12

nQ2 nQ 2X 1X Y 12 nQ 1nQ

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

X

0

X

0

0

X

0

1

0

0

0

1

0

0

0

0

X

0

X

0

1

X

1

1

1

0

1

1

1

0

0

1

X

0

X

1

0

X

1

1

1

0

1

1

1

Para Qn+2:

nnnn QXQXXQQnQ ..).(12 12212

Comparando:

2222 ..12 JQKQnQnn

nQXJ .12

13

212 .. XXQK n

Para Qn+1:

)()....(1 22122221 nnnn QXQXXQXXXQQn

)().(1 222221 nnnn QXQQXXXQQn

Comparando:

2222 ..1 JQKQQnnn

nQXJ 221

nQXXXK 22211 .

Para Y:

14

122 .. XXQY n

J4

Q15

CLK1

K16

Q14

S2

R3

U1:A

74LS76

J9

Q11

CLK6

K12

Q10

S7

R8

U1:B

74LS76

0

X1

0

X2

1

2

3

U2:A

74LS32

1

2

3

U3:A

74LS86

1 2

U4:A

74LS04

1

2

3

U5:A

74LS08

3 4

U4:B

74LS044

5

6

U5:B

74LS08

9

10

8

U5:C

74LS08

5 6

U4:C

74LS04

13 12

U4:D

74LS04

1

2

13

12

U6:A

74LS11

3

4

5

6

U6:B

74LS11

8.-

15

A) para la Tabla 1

i) Corresponde a un FSM Mealy, ya que las salidas dependen de las entradas y sus

estados.

ii) Diseñando el grafo de la tabla 1

iii) Ahora utilizando FF-JK

Los Estados {D,C,B,A} ={ 3S , 2S , 1S , 0S }={11,10,01,00}

Las entradas {x}= {0,1}

nQ2 nQ x y 12 nQ 1nQ

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

1

1

1

0

1

0

1

0

1

0

0

0

1

1

0

0

1

1

1

0

1

0 1

A B.0 C.0

B A.0 D.1

C B.1 B.1

D A.0 D.1

16

a) Utilizando FF- JK

Para Q2n+1 :

XQQXQnQnnn ...12

22

Comparando:

2222 ..12 JQKQnQnn

nQXK

XJ

2

2

Para Qn+1 :

)(.1 2nnn QXQXQQn

Comparando:

XK

XQJ n

1

21

Para Y:

11 ..1 JQKQQnnn

17

nnn QQXQY 2.

J4

Q15

CLK1

K16

Q14

S2

R3

U1:A

74LS76

J9

Q11

CLK6

K12

Q10

S7

R8

U1:B

74LS76

0

X

1

2

3

U2:A

74LS32

5 6

U4:C

74LS04

4

5

6

U2:B

74LS32

1

2

3

U3:A

74LS08

4

5

6

U3:B

74LS08

9

10

8

U2:C

74LS32

b) Utilizando FF-T

Convertiremos de un FF-T a un FF-JK

J K nQ 1nQ T

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

0

0

1

1

1

0

0

0

0

1

1

0

1

1

18

nnQKQJT ..

B) Para la Tabla 2

00 01 10 11

A A.0 D.0 A.0 D.0

B D.0 B.1 D.0 D.0

C A.0 C.1 D.0 D.0

D D.0 D.0 A.0 D.0

i) Es un FSM de Mealy

ii) Haciendo el grafo de la tabla 2

iii) Los Estados {D,C,B,A} ={ 3S , 2S , 1S , 0S }={11,10,01,00}

Las entradas { 12 , XX }= {00,01,10,11}

Se utiliza 2 FF-JK

19

nQ2 nQ 2X 1X Y 12 nQ 1nQ

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

1

1

0

1

1

0

1

1

1

1

1

0

1

0

1

0

1

1

1

1

1

0

0

1

1

1

1

0

1

a) Utilizando FF- JK

Para Qn+2 :

)...()..(12 121122122 XXXQXQQQXXXQQnQnnnnnn

).()(12 1212122 XXXQQXXQQnQ nnnn

Comparando:

JQKQnQnn ..12

22

1212 .XXXQJ n

20

Para Qn+1:

)..()..(1 221221121 XQXQQXXXQXQQn nnnnn

Comparando:

JQKQQnnn ..1

)..().(

)..(

211211

22121

XXXQXK

XQXQJ

n

nn

Para Y:

122122...... XXQQXXQQY

nnnn

)(. 212 nn QQXXY

122 .XXQK n

21

J4

Q15

CLK1

K16

Q14

S2

R3

U1:A

74LS76

J9

Q11

CLK6

K12

Q10

S7

R8

U1:B

74LS76

0

X1

4

5

6

U5:B

74LS08

9

10

8

U5:C

74LS08

5 6

U4:C

74LS04

0

X2

1

2

3

U2:A

74LS08

1

2

3

U3:A

74LS32

9

10

11

8

U6:C

74LS11

4

5

6

U3:B

74LS32

1

2

3

U7:A

74LS86

4

5

6

U2:B

74LS08

9

10

8

U3:C

74LS32

4

5

6

U7:B

74LS86

1 2

U4:A

74LS04

9

10

8

U2:C

74LS08

9

10

8

U7:C

74LS86

1

2

13

12

U6:A

74LS113 4

U4:B

74LS04

b) Utilizando FF-T

Convertiremos de un FF-T a un FF-JK

J K nQ 1nQ T

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

0

0

1

1

1

0

0

0

0

1

1

0

1

1

nnQKQJT ..

22

C) Para la Tabla 3

i) Es un FSM Mealy

ii) Diseñando su grafo.

iii) Los Estados {D,C,B,A} ={ 3S , 2S , 1S , 0S }={11,10,01,00}

Las entradas {X}= {0,1}

Se utiliza 2 FF-JK

0 1

A B.0 B.0

B C.0 A.1

C B.0 D.0

D C.0 B.1

nQ2 nQ x y 12 nQ 1nQ

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0

0

1

0

0

0

1

0

0

1

0

0

1

1

0

1

1

1

0

1

1

0

1

23

a) Utilizando FF- JK

Para Q2n+1:

nnnnn QXQXQXQQnQ ..)..(1222

Ahora Comparando:

JQKQnQnn 2212

XQK

QXJ

n

n

2

2 .

Para Qn+1:

nnnn QXQXQQQn )..(1 22

Comparando:

JQKQQn nn .1

24

XQK

J

n

21

1 1

Para Y:

nQXY .

J4

Q15

CLK1

K16

Q14

S2

R3

U1:A

74LS76

J9

Q11

CLK6

K12

Q10

S7

R8

U1:B

74LS76

0

X

5 6

U4:C

74LS04

1

2

3

U7:A

74LS86

1

2

3

U2:A

74LS08

1

2

3

U5:A

74LS86

1 2

U3:A

74LS04

4

5

6

U2:B

74LS08

b) Utilizando FF-T

Convertiremos de un FF-T a un FF-JK

J K nQ 1nQ T

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

0

0

1

1

1

0

0

0

0

1

1

0

1

1

25

nnQKQJT ..

D) Para la Tabla 4

i) Es un FSM Mealy

ii) Diseñando su grafo.

iii) Los Estados {D,C,B,A} ={ 3S , 2S , 1S , 0S }={11,10,01,00}

Las entradas {X}= {0,1}

Se utiliza 2 FF-JK

0 1

A D.1 B.0

B D.0 B.0

C C.0 A.1

D A.0 C.0

26

1º y 2º FF-JK = { nn QQ ,2 }

a) Utilizando FF- JK

Para Q2n+1:

)..(.12 22 nnnn QXQXQXQnQ

Comparando ahora:

2222 .12 KQJQnQ nn

nQXK

XJ

2

2

Para Qn+1:

nQ2 nQ x y 12 nQ 1nQ

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

0

0

1

0

1

0

0

1

0

1

0

1

0

0

0

1

1

1

1

0

0

0

0

27

nnnn QQQQQn22

..1

Comparando ahora:

JQKQQnnn .1

n

n

QK

QJ

21

21

Para Y:

)(

....

2

22

nn

nnnn

QXQY

QXQQXQY

J4

Q15

CLK1

K16

Q14

S2

R3

U1:A

74LS76

J9

Q11

CLK6

K12

Q10

S7

R8

U1:B

74LS76

0

X

5 6

U4:C

74LS04

1

2

3

U2:A

74LS86

4

5

6

U2:B

74LS86

1 2

U3:A

74LS04

28

b) Utilizando FF-T

Convertiremos de un FF-T a un FF-JK

J K nQ 1nQ T

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

0

0

1

1

1

0

0

0

0

1

1

0

1

1

nnQKQJT ..

E) Para la Tabla 5

i) Es un FSM es de tipo FSM Mealy

ii) Diseñando su grafo.

0 1

A C.0 A.0

B B.0 A.0

C D.1 C.1

D D.0 B.0

E C.1 A.0

29

iii) Los Estados {E,D,C,B,A} ={ 4S , 3S , 2S , 1S , 0S }={100,011,010,001,000}

Las entradas {X}= {0,1}

Se utiliza 2 FF-JK

1º , 2º y 3º FF-JK = { nnn QQQ ,, 23 }

nQ3 nQ2 nQ X Y 13 nQ 12 nQ 1nQ

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

1

1

0

0

1

0

X

X

X

X

X

X

0

0

0

0

0

0

0

0

0

0

X

X

X

X

X

X

1

0

0

0

1

1

1

0

1

0

X

X

X

X

X

X

1

0

1

0

1

0

1

1

0

0

X

X

X

X

X

X

30

a) Utilizando FF- JK

Para Q3n+1:

013 nQ

Comparando:

0.013 3.3 nn QQnQ

1

0

3

3

K

J

Para Q2n+1:

31

)..()(1222 XQQQXQnQ

nnnn

Comparando:

JQKQnQnn ..12

222

n

n

QXK

QXJ

.

.

2

2

Para Qn+1:

)(..1 23XQQQXQQn nnnn

Comparando:

JQKQQnnn .1 1

XQK

QXJ

n

n

.

.

21

31

Para Y:

32

nnnn QXQQQY 32 ..

J4

Q15

CLK1

K16

Q14

S2

R3

U1:A

74LS76

J9

Q11

CLK6

K12

Q10

S7

R8

U1:B

74LS76

0

X

5 6

U4:C

74LS04

J4

Q15

CLK1

K16

Q14

S2

R3

U5:A

74LS76

1

2

3

U6:A

74LS08

4

5

6

U6:B

74LS08

1

2

3

U2:A

74LS08

4

5

6

U2:B

74LS08

1

2

13

12

U3:A

74LS11

9

10

8

U2:C

74LS08

1

2

3

U7:A

74LS32

b) Utilizando FF-T

Convertiremos de un FF-T a un FF-JK

J K nQ 1nQ T

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

0

1

0

0

1

1

1

0

0

0

0

1

1

0

1

1

nnQKQJT ..

33

9.-

Solución:

A)

En el circuito dado en la pregunta numero 10, es un circuito tipo de maquina de estado

MEALY, por consiguiente vemos en la figura que las entradas del registro dependen

de las salidas de la memoria.

34

B)

SB Qn Qn+1

0 0 0 0 0 0 1

1 0 0 0 1 1 0

0 0 0 1 0 1 1

1 0 0 1 0 0 0

0 0 1 0 1 0 0

1 0 1 0 1 1 1

0 0 1 1 1 0 1

1 0 1 1 0 0 1

0 1 0 0 1 1 0

1 1 0 0 0 1 0

0 1 0 1 1 1 1

1 1 0 1 0 1 1

0 1 1 0 0 0 0

1 1 1 0 1 0 0

0 1 1 1 0 1 0

1 1 1 1 1 0 1

Diagrama de estados

δ (0 , 000 ) = 001

δ (1 , 000 ) = 110

δ (0 , 001 ) = 011

δ (1 , 001) = 000

δ (0 , 010) = 100

δ (1 , 010 ) = 111

δ (0 , 011 ) = 101

δ (1 , 011) = 001

δ (0 , 100 ) = 110

δ (1 , 100 ) = 010

δ (0 , 101 ) = 111

δ (1 , 101) = 011

δ (0 , 110 ) = 000

δ (1 , 110 ) = 100

δ (0 , 111) = 010

δ (1 , 111 ) = 101

35

C) Vemos en el grafico de MEALY del circuito, para que el circuito evolucione del

estado 0 al estado 5 se necesitamos 4 ciclos de reloj, ya que el circuito empieza

por el estado 1, debemos regresarlo al estado al estado 0 con SB=1 (1er clock),

regresamos al estado 1 con SB=0 (2do clock), al estado 3 con SB=0 (3er clock) y

al estado 5 con SB=0 (4to clock).

Fig. 7 (Diseño de un contador con estado de memoria)

Fig. 8 (Diagrama de tiempo del circuito)

D) Representaremos el circuito (ROM 16x3) con un EPROM 27C32 (32Kx8) con la

siguiente programación correspondiente a la ROM 16x3.

36

Dirección Dato

000h 00000001

001h 00000110

002h 00000011

003h 00000000

004h 00000100

005h 00000111

006h 00000101

007h 00000001

008h 00000110

009h 00000010

00Ah 00000111

00Bh 00000011

00Ch 00000000

00Dh 00000100

00Eh 00000010

00Fh 00000101

010h-

FFFh

00000000

10.-

Analizaremos el circuito asumiendo el control del multiplexor 01 CyC igual a:

00 01 CC

CLOCK 0Z 1Z

↑ 0 1

↑ 1 0

↑ 1 1

↑ 0 0

↑ 1 0

37

10 01 CC

CLOCK 0Z 1Z

↑ 1 1

↑ 0 1

↑ 1 0

↑ 0 0

01 01 CC

0Z 1Z

0 0

11 01 CC 00 01 DD

11 01 CC 00 01 DD

11 01 CC 00 01 DD

CLOCK 0Z 1Z

↑ 1 1

↑ 0 1

11 01 CC 11 01 DD

CLOCK 0Z 1Z

↑ 1 0

↑ 0 0

0Z 1Z

0 0

0Z 1Z

0 1

38

Ahora sustituyamos el biestable T por el biestable JK.

Tabla de estado de FF-JK

Tabla de habilitación del FF-T

Tabla de conversión del FF-T a FF-JK

J K q Q

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 1

q Q T

0 0 0

0 1 1

1 0 1

1 1 0

J K q Q T

0 0 0 0 0

0 0 1 1 0

0 1 0 0 0

0 1 1 0 1

1 0 0 1 1

1 0 1 1 0

1 1 0 1 1

1 1 1 0 1

39

Hallando la conversión del FF-T a FF-JK a través del mapas de Karnaugh

J

1 1 1 0 K

1 0 0 0

Q Q Q

La función T es:

KQQJT

Finalmente el diseño queda:

Fig. 9 (Circuito modificado, sustitución del biestable T por el biestable JK)

![Q KV CLT Q Njr|jŒr« $mîo GKly D-cuŸu~u XI†ŒlSrimages.mathrubhumi.com/pdf/muhammedans_club.pdf · Q kv-t]m-À-Svkv Q al-ò-`q-ar- |r.](https://static.fdocumentos.tips/doc/165x107/5ecbe51fd9f86a4fd26b3da6/q-kv-clt-q-njrjr-mo-gkly-d-cuuu-xia-q-kv-tm-svkv-q-al-q-ar-.jpg)

![SISTEMAS DIGITAIS - ULisboa...G5 C6 / 2, 3, 5 + / 2, 4, 5 - 3, 5CT=7 [2] [4] 1, 6D M 3 M 4 4, 5CT=0 1D C1 1R Q Q INI INI CLK CLK 1 Q0 Q1 Q2 1J C1 1K Q CLK CLK2 INI 1R Y 1 Y 3 Y 0 Y](https://static.fdocumentos.tips/doc/165x107/60825455f539cb25df64014e/sistemas-digitais-ulisboa-g5-c6-2-3-5-2-4-5-3-5ct7-2-4-1.jpg)