ON MANY-CORE PROCESSORS AND PERFORMANCE … · ON MANY-CORE PROCESSORS Inaugural-Disseration zur...

Transcript of ON MANY-CORE PROCESSORS AND PERFORMANCE … · ON MANY-CORE PROCESSORS Inaugural-Disseration zur...

I N F O R M AT I K

I M P R O V I N G P R O G R A M M A B I L I T YA N D P E R F O R M A N C E P O RTA B I L I T Y

O N M A N Y- C O R E P R O C E S S O R S

Inaugural-Disserationzur Erlangung des Doktorgrades derNaturwissenschaften im Fachbereich

Mathematik und Informatikder Mathematisch-Naturwissenschaftlichen Fakultät

der Westfälischen Wilhelms-Universität Münster

vorgelegt von

michel steuwer

aus Duisburg

– 2015 –

I N F O R M AT I K

I M P R O V I N G P R O G R A M M A B I L I T YA N D P E R F O R M A N C E P O RTA B I L I T Y

O N M A N Y- C O R E P R O C E S S O R S

Inaugural-Disserationzur Erlangung des Doktorgrades derNaturwissenschaften im Fachbereich

Mathematik und Informatikder Mathematisch-Naturwissenschaftlichen Fakultät

der Westfälischen Wilhelms-Universität Münster

vorgelegt von

michel steuwer

aus Duisburg

– 2015 –

1.1 multi-core processors and their programming 5

●●●●●●

●

●●● ●●

●

●●●●●●●

●●●● ●●● ●

● ●● ● ●●●● ●●●●●●● ●●

●● ●●● ●●●●●●●● ●

●●●●●●●●●●●

●●●●●●●●

●●●●●●

●●●●●●●●●●●●●●●● ●●●●●●●●●

●●●●●●●●

●●●●●

●●●●●●

●●●●●●●●●●●●●●●●●●●●●●●●●

●●●●●●●● ●

●●●●

●●●●●

●●●

●●●●

●●●●●●●●●●● ●

● ●

●●●● ●

●●

1

10

100

1,000

10,000

100,000

1,000,000

10,000,000

1970 1975 1980 1985 1990 1995 2000 2005 2010 2015

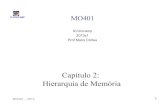

● Transistors (in 1000s)Clock Frequency (in Mhz)Power (in Watt)Number of Cores

Figure 1.1: Development of Intel Desktop CPUs over time. While transistorcount continues to grow, around 2005 clock frequency and powerconsumption have reached a plateau. As an answer multi-coreprocessors emerged. Inspired by [145].

and increased heat development. This has led to architectures whichparticularly focus on their energy efficiency, the most prominent ex-ample of such architectures are modern graphics processing units(GPUs). Originally developed for accelerating the rendering of com-plex graphics and 3D scenes, GPU architectures have been recentlygeneralized to support more types of computations. Some people re-fer to this development using the term general-purpose computingon graphics processing units (GPGPU).

Technically GPU architectures are multi-core architectures like mod-ern multi-core CPUs, but each individual core on a GPU typically hasdozens or hundreds of functional units which can perform computa-tions in parallel following the Single Instruction, Multiple Data (SIMD)principle. These types of architectures are optimized towards a highthroughput of computations, therefore, they focus on performing alarge amount of operations in parallel and feature no, or only small,caches to prevent or mitigate latencies of the memory: if a threadstalls waiting for the memory, another thread takes over and keepsthe core busy. For multi-core CPUs switching between threads is moreexpensive, therefore, CPUs are instead optimized to avoid long laten-cies when accessing the memory with a deep cache hierarchy andadvanced architectural features, like long pipelines and out-of-orderexecution, all of which are designed to keep each core busy.

Die Manycore Ära

Inspiriert von Herb Sutter “The Free Lunch is Over: A Fundamental Turn Towards

Concurrency in Software”

Intel CPUs von 1970 bis 2015

multicore CPUs

GPUs

FPGAsBeschleuniger

Die Manycore Ära

I. Die Herausforderung der Programmierbarkeit

II. Die Herausforderung der Performance-Portabilität

Agenda

Meine Dissertation adressiert zwei zentrale Herausforderungen:

TEIL IDie Herausforderung der Programmierbarkeit

Programmierung mit OpenCL

kernel void reduce(global float* g_idata, global float* g_odata, unsigned int n, local float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_global_id(0); l_data[tid] = (i < n) ? g_idata[i] : 0; barrier(CLK_LOCAL_MEM_FENCE); // do reduction in local memory for (unsigned int s=1; s < get_local_size(0); s*= 2) { if ((tid % (2*s)) == 0) { l_data[tid] += l_data[tid + s]; barrier(CLK_LOCAL_MEM_FENCE); } } // write result for this work-group to global memory if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

• Beispiel: Parallele Summation eines Arrays in OpenCL

Programmierung mit OpenCL

kernel void reduce(global float* g_idata, global float* g_odata, unsigned int n, local float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_global_id(0); l_data[tid] = (i < n) ? g_idata[i] : 0; barrier(CLK_LOCAL_MEM_FENCE); // do reduction in local memory for (unsigned int s=1; s < get_local_size(0); s*= 2) { if ((tid % (2*s)) == 0) { l_data[tid] += l_data[tid + s]; barrier(CLK_LOCAL_MEM_FENCE); } } // write result for this work-group to global memory if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

• Beispiel: Parallele Summation eines Arrays in OpenCL

Kernel Funktion wird parallel von vielen work-items ausgeführt

Work-items werden durch eine globale id identifizier

Programmierung mit OpenCL

kernel void reduce(global float* g_idata, global float* g_odata, unsigned int n, local float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_global_id(0); l_data[tid] = (i < n) ? g_idata[i] : 0; barrier(CLK_LOCAL_MEM_FENCE); // do reduction in local memory for (unsigned int s=1; s < get_local_size(0); s*= 2) { if ((tid % (2*s)) == 0) { l_data[tid] += l_data[tid + s]; barrier(CLK_LOCAL_MEM_FENCE); } } // write result for this work-group to global memory if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

• Beispiel: Parallele Summation eines Arrays in OpenCL

Work-items werden zu work-groups zusammengefasst Lokale id innerhalb einer work-group

Programmierung mit OpenCL

kernel void reduce(global float* g_idata, global float* g_odata, unsigned int n, local float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_global_id(0); l_data[tid] = (i < n) ? g_idata[i] : 0; barrier(CLK_LOCAL_MEM_FENCE); // do reduction in local memory for (unsigned int s=1; s < get_local_size(0); s*= 2) { if ((tid % (2*s)) == 0) { l_data[tid] += l_data[tid + s]; barrier(CLK_LOCAL_MEM_FENCE); } } // write result for this work-group to global memory if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

• Beispiel: Parallele Summation eines Arrays in OpenCL

Großer, aber langsamer globaler Speicher Kleiner, aber schneller lokaler Speicher

Barrieren für Speicherkonsistenz

Programmierung mit OpenCL

kernel void reduce(global float* g_idata, global float* g_odata, unsigned int n, local float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_global_id(0); l_data[tid] = (i < n) ? g_idata[i] : 0; barrier(CLK_LOCAL_MEM_FENCE); // do reduction in local memory for (unsigned int s=1; s < get_local_size(0); s*= 2) { if ((tid % (2*s)) == 0) { l_data[tid] += l_data[tid + s]; } barrier(CLK_LOCAL_MEM_FENCE); } // write result for this work-group to global memory if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

• Beispiel: Parallele Summation eines Arrays in OpenCL

Funktional korrekte Implementierungen in OpenCL sind schwierig!

DAS SKELCLPROGRAMMIERMODEL

Das SkelCL Programmiermodel

• Parallele Datencontainer für eine einheitliche Speicherverwaltung zwischen CPU und (mehreren) GPUs

• implizite Speichertransfers zwischen CPU und GPU • lazy copying minimiert den Datentransfer

• Wiederkehrende Muster paralleler Programmierung (Algorithmische Skelette) für eine vereinfachte Beschreibung paralleler Berechnungen

• Daten Verteilungenfür einen transparenten Datentransfer in Systemen mit mehreren GPUs.

Drei Abstraktionen zu OpenCL hinzugefügt:

zip (⊕) [x1, …, xn] [y1, …, yn] = [x1 ⊕ y1, …, xn ⊕ yn] reduce (⊕) ⊕id [x1, …, xn] = ⊕id ⊕ x1 ⊕ … ⊕ xn

CPU

GPUs0 1

CPU

GPUs0 1

CPU

GPUs0 1

single copy block

Die SkelCL Softwarebibliothek am Beispiel

#include <SkelCL/SkelCL.h>#include <SkelCL/Zip.h>#include <SkelCL/Reduce.h>#include <SkelCL/Vector.h>

float dotProduct(const float* a, const float* b, int n) { using namespace skelcl; skelcl::init( 1_device.type(deviceType::ANY) ); auto mult = zip([](float x, float y) { return x*y; }); auto sum = reduce([](float x, float y) { return x+y; }, 0); Vector<float> A(a, a+n); Vector<float> B(b, b+n); Vector<float> C = sum( mult(A, B) ); return C.front();}

dotProduct A B = reduce (+) 0 (zip (⨉) A B)

Neue Algorithmische Skelette

3.2 the skelcl programming model 43

Figure 3.5: Visualization of the Gaussian blur stencil application.

into account. When neighboring elements are accesses at the bound-aries of the container out-of-bound accesses occur. In these cases thefunction h is called with the index causing the out-of-bound accessand returns a replacement value. We now formally define the stencilskeleton. We start with the definition for vectors:

definition 3.7. Let ~x be a vector of size n with elements xi

where 0 < i 6n. Let f be an unary customizing function, d be a positive integer value, andh be an out-of-bound handling function. The algorithmic skeleton stencil isdefined as follows:

stencil f d h [x1

, x2

, . . . , xn

]def= [y

1

,y2

, . . . ,yn

]

where

yi

= f [xi-d

, . . . , xi+d

] 8 i : 0 < i 6 n

andxj

= h j 8 j : -d < j 6 0 _n < j 6 n+ d.

The definition for matrices is similar:

definition 3.8. Let M be an n⇥m matrix with elements mi,j where 0 <

i 6 n and 0 < j 6 m. Let f be an unary customizing function, d bean positive integer value, and h be an out-of-bound handling function. Thealgorithmic skeleton stencil is defined as follows:

stencil f d h

2

64m

1,1 · · · m1,m......

mn,1 · · · m

n,m

3

75def=

2

64n1,1 · · · n

1,m......

nn,1 · · · n

n,m

3

75

where

ni,j = f

2

64m

i-d,j-d

· · · mi-d,j+d...

...m

i+d,j-d

· · · mi+d,j+d

3

75 8 i, j0 < i 6 n,0 < j 6 m

and

46 high-level programming for multi-gpu systems

A

B

C

BT

1

2

3

(a)

A

BT

C

1

2

3

(b)

Figure 3.7: The allpairs computation schema. (a): element c2,3 3 is com-

puted by combining the second row of A 1 with the third rowof B 2 using the binary operator �. (b): the same situation wherethe transpose of matrix B is shown.

Figure 3.7a illustrates this definition: the element c2,3 of matrix C

marked as 3 is computed by combining the second row of A markedas 1 with the third row of B marked as 2 using the binary opera-tor �. Figure 3.7b shows the same computation with the transposedmatrix B. This visualization shows how the structure of matrix C isdetermined by the two input matrices A and B.

Let us consider two example applications which can be expressedby customizing the allpairs skeleton with a particular function �.

example 1 : The Manhattan distance (or L1

distance) is a measureof distance which is used in many applications. In general, it is de-fined for two vectors, ~x and ~y, of equal length d, as follows:

ManDist ~x ~y =dX

k=1

|xk

- yk

| (3.2)

In [31], the so-called Pairwise Manhattan Distance (PMD) is studiedas a fundamental operation in hierarchical clustering for data analy-sis. PMD is obtained by computing the Manhattan distance for everypair of rows of a given matrix. This computation for arbitrary matrixA can be expressed using the allpairs skeleton customized with theManhattan distance defined in Equation (3.2):

PMD A = allpairs ManDist A A (3.3)

The n⇥ n matrix computed by the customized skeleton contains theManhattan distance for every pair of rows of the input n⇥ d matrixA.

example 2 : Matrix multiplication is a basic linear algebra opera-tion, which is a building block of many scientific applications. A n⇥d

Stencil Berechnungen Allpairs Berechnungen

A ⨉ B = allpairs dotProduct A BT

dotProduct a b = zipReduce (+) 0 (⨉) a b

gauss M = stencil f 1 0 M

wo f die Funktion is welche den Gaußschen Weichzeichnerbeschreibt

CPU

GPUs0 1

overlap Verteilung

Beispiel: Gaußscher Weichzeichner

Unterstützung für mehre GPUs:

Example:Matrix Multiplication

Optimierung für zipReduce Muster:

Unterstützung für mehrere GPUs mitblock und copy Verteilung

SkelCL Evaluation — Geschwindigkeit

4.8 summary 113

mandelbrot linear algebra(dot product)

matrixmultiplication

image processing(gaussian blur)

medical imaging(LM OSEM)

0.000.15

0.50

1.00

OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL

Rela

tive

Line

s of

Cod

e

CPU code GPU code

Figure 4.23: Relative lines of code for five application examples discussed inthis chapter comparing OpenCL code with SkelCL code.

mandelbrot linear algebra(dot product)

matrixmultiplication

image processing(gaussian blur)

medical imaging(LM OSEM)

physics simulation(FDTD)

0.0

0.5

1.0

1.5

2.0

OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL

Rela

tive

Runt

ime

Figure 4.24: Relative runtime for six application examples discussed inthis chapter comparing OpenCL-based implementations withSkelCL-based implementations.

the right). We scaled all graphs relative to the lines of code required bythe OpenCL implementation. The SkelCL code is significant shorter inall cases, requiring less than 50% of the lines of code of the OpenCL-based implementation. For the linear algebra application, matrix mul-tiplication, and image processing application even less than 15% oflines of code are required when using SkelCL.

Figure 4.24 shows the runtime results for six of the applicationexamples presented in this chapter. We compare the runtime of op-timized OpenCL implementations against SkelCL-based implementa-tions. For all shown application examples – except the dot productapplication – we can see that SkelCL is close to the performance ofthe OpenCL implementations. For most applications the runtime ofthe SkelCL-based implementations are within 10% of the OpenCL im-plementations. For the matrix multiplication SkelCL is 33% slowerthan the optimized OpenCL implementation which only operates onsquared matrices. The dot product application is significantly slower,as SkelCL generates two separate OpenCL kernels instead of a singleoptimized kernel.

SkelCL nahe an der Geschwindigkeit von OpenCL!(Ausnahme: dot product … mehr dazu in Teil II)

SkelCL Evaluation — Produktivität4.8 summary 113

mandelbrot linear algebra(dot product)

matrixmultiplication

image processing(gaussian blur)

medical imaging(LM OSEM)

0.000.15

0.50

1.00

OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL

Rela

tive

Line

s of

Cod

e

CPU code GPU code

Figure 4.23: Relative lines of code for five application examples discussed inthis chapter comparing OpenCL code with SkelCL code.

mandelbrot linear algebra(dot product)

matrixmultiplication

image processing(gaussian blur)

medical imaging(LM OSEM)

physics simulation(FDTD)

0.0

0.5

1.0

1.5

2.0

OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL OpenCL SkelCL

Rela

tive

Runt

ime

Figure 4.24: Relative runtime for six application examples discussed inthis chapter comparing OpenCL-based implementations withSkelCL-based implementations.

the right). We scaled all graphs relative to the lines of code required bythe OpenCL implementation. The SkelCL code is significant shorter inall cases, requiring less than 50% of the lines of code of the OpenCL-based implementation. For the linear algebra application, matrix mul-tiplication, and image processing application even less than 15% oflines of code are required when using SkelCL.

Figure 4.24 shows the runtime results for six of the applicationexamples presented in this chapter. We compare the runtime of op-timized OpenCL implementations against SkelCL-based implementa-tions. For all shown application examples – except the dot productapplication – we can see that SkelCL is close to the performance ofthe OpenCL implementations. For most applications the runtime ofthe SkelCL-based implementations are within 10% of the OpenCL im-plementations. For the matrix multiplication SkelCL is 33% slowerthan the optimized OpenCL implementation which only operates onsquared matrices. The dot product application is significantly slower,as SkelCL generates two separate OpenCL kernels instead of a singleoptimized kernel.

SkelCL Programme sind signifikant kürzer!

TEIL IIDie Herausforderung der Performance-Portabilität

EIN NEUER ANSATZ ZURPERFORMANCE PORTABLEN

CODEGENERIERUNG

OpenCL und Performance-Portabilität

130 code generation using patterns

Hardware Bandwidth Limit

0

50

100

150

200

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

cuBLA

S

Band

wid

th (G

B/s)

(a) Nvidia’s GTX 480 GPU.

Hardware Bandwidth Limit

0

100

200

300

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

clBLA

S

Band

wid

th (G

B/s)

(b) AMD’s HD 7970 GPU.

Hardware Bandwidth Limit

Failed Failed Failed0

10

20

30

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7MKL

Band

wid

th (G

B/s)

(c) Intel’s E5530 dual-socket CPU.

Figure 5.2: Performance of differently optimized implementations of theparallel reduction

• Beispiel: Parallele Summation eines Arrays in OpenCL

• Vergleich von 7 OpenCL Implementierungen von Nvidia

130 code generation using patterns

Hardware Bandwidth Limit

0

50

100

150

200

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

cuBLA

S

Band

wid

th (G

B/s)

(a) Nvidia’s GTX 480 GPU.

Hardware Bandwidth Limit

0

100

200

300

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

clBLA

S

Band

wid

th (G

B/s)

(b) AMD’s HD 7970 GPU.

Hardware Bandwidth Limit

Failed Failed Failed0

10

20

30

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7MKL

Band

wid

th (G

B/s)

(c) Intel’s E5530 dual-socket CPU.

Figure 5.2: Performance of differently optimized implementations of theparallel reduction

130 code generation using patterns

Hardware Bandwidth Limit

0

50

100

150

200

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

cuBLA

S

Band

wid

th (G

B/s)

(a) Nvidia’s GTX 480 GPU.

Hardware Bandwidth Limit

0

100

200

300

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

clBLA

S

Band

wid

th (G

B/s)

(b) AMD’s HD 7970 GPU.

Hardware Bandwidth Limit

Failed Failed Failed0

10

20

30

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7MKL

Band

wid

th (G

B/s)

(c) Intel’s E5530 dual-socket CPU.

Figure 5.2: Performance of differently optimized implementations of theparallel reduction

130 code generation using patterns

Hardware Bandwidth Limit

0

50

100

150

200

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

cuBLA

S

Band

wid

th (G

B/s)

(a) Nvidia’s GTX 480 GPU.

Hardware Bandwidth Limit

0

100

200

300

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7

clBLA

S

Band

wid

th (G

B/s)

(b) AMD’s HD 7970 GPU.

Hardware Bandwidth Limit

Failed Failed Failed0

10

20

30

Impl.

1Im

pl. 2

Impl.

3Im

pl. 4

Impl.

5Im

pl. 6

Impl.

7MKL

Band

wid

th (G

B/s)

(c) Intel’s E5530 dual-socket CPU.

Figure 5.2: Performance of differently optimized implementations of theparallel reductionPerformance in OpenCL ist nicht portabel!

• Beispiel: Parallele Summation eines Arrays in OpenCL

• Vergleich von 7 OpenCL Implementierungen von Nvidia

OpenCL und Performance-Portabilität

134 code generation using patterns

High-level Expression

OpenCL Program

OpenCL Patterns

Algorithmic Patterns

Low-level Expression

Algorithmic choices &Hardware optimizations

map

reduce

iterate

split

join

vectorize toLocal

map-local

map-workgroup

vector units

workgroups

local memory

barriers

...Dot product Vector reduction

Hardware Paradigms

Code generation

High-levelprogramming

reorder...

...

...

Exploration withrewriting rules

BlackScholes

Figure 5.3: Overview of our code generation approach. Problems expressedwith high-level algorithmic patterns are systematically trans-formed into low-level OpenCL patterns using a rule rewritingsystem. OpenCL code is generated by mapping the low-level pat-terns directly to the OpenCL programming model representinghardware paradigms.

We argue that the root of the problem lies in a gap in the systemstack between the high-level algorithmic patterns on the one handand low-level hardware optimizations on the other hand. We proposeto bridge this gap using a novel pattern-based code generation tech-nique. A set of rewrite rules systematically translates high-level algo-rithmic patterns into low-level hardware patterns. The rewrite rulesexpress different algorithmic and optimization choices. By systemati-cally applying the rewrite rules semantically equivalent, low-level ex-pressions are derived from high-level algorithm expressions writtenby the application developer. Once derived, high-performance codebased on these expressions can be automatically generated. The nextsection introduces an overview of our approach.

5.2 overview of our code generation approach

The overview of our pattern-based code generation approach is pre-sented in Figure 5.3. The programmer writes a high-level expressioncomposed of algorithmic patterns. Using a rewrite rule system, wetransform this high-level expression into a low-level expression consist-ing of OpenCL patterns. At this rewrite stage, algorithmic and opti-mization choices in the high-level expression are explored. The gen-erated low-level expression is then fed into our code generator thatemits an OpenCL program which is, finally, compiled to machine code

Performance portable Codegenerierung mit Transformationsregeln

kernel void reduce6(global float* g_idata, global float* g_odata, unsigned int n, local volatile float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_group_id(0) * (get_local_size(0)*2) + get_local_id(0); unsigned int gridSize = WG_SIZE * get_num_groups(0); l_data[tid] = 0; while (i < n) { l_data[tid] += g_idata[i]; if (i + WG_SIZE < n) l_data[tid] += g_idata[i+WG_SIZE]; i += gridSize; } barrier(CLK_LOCAL_MEM_FENCE);

if (WG_SIZE >= 256) { if (tid < 128) { l_data[tid] += l_data[tid+128]; } barrier(CLK_LOCAL_MEM_FENCE); } if (WG_SIZE >= 128) { if (tid < 64) { l_data[tid] += l_data[tid+ 64]; } barrier(CLK_LOCAL_MEM_FENCE); } if (tid < 32) { if (WG_SIZE >= 64) { l_data[tid] += l_data[tid+32]; } if (WG_SIZE >= 32) { l_data[tid] += l_data[tid+16]; } if (WG_SIZE >= 16) { l_data[tid] += l_data[tid+ 8]; } if (WG_SIZE >= 8) { l_data[tid] += l_data[tid+ 4]; } if (WG_SIZE >= 4) { l_data[tid] += l_data[tid+ 2]; } if (WG_SIZE >= 2) { l_data[tid] += l_data[tid+ 1]; } } if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

164 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 join � map-warp

�

4 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 1 �5 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 2 �6 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 4 �7 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 8 �8 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 16 �9 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 32

10

�� split 64 �

11 join � map-local (reduce-seq (+) 0) � split 2 � reorder-stride 64 �12 join � toLocal (map-local (reduce-seq (+) 0)) �13 split (blockSize/128) � reorder-stride 12814

�� split blockSize

Listing 5.13: Expression resembling the seventh implementation of parallelreduction presented in Listing 5.7.

Before we look at how OpenCL code is generated, we discuss oneadditional optimization: fusion of patterns.

5.4.3.3 Systematic Fusion of Patterns

Back in Chapter 4 in Section 4.3 we discussed how the sum of ab-solute values (asum) can be implemented in SkelCL. Two algorithmicskeletons, reduce and map, were composed to express this applicationas shown in Equation (5.17).

asum ~x = reduce (+) 0�

map (| . |) ~x�

(5.17)

where: |a| =

�a if a > 0

-a if a < 0

When evaluating the performance of the SkelCL implementation, weidentified a problem: SkelCL treats each algorithmic skeleton sepa-rately, thus, forcing the map skeleton to write a temporary array backto global memory and then read it again for the next computation,which greatly reduces performance. The temporary array could beavoided, but in the library approach followed by SkelCL it is difficultto implement a generic mechanism for fusing algorithmic skeletons.

By using our pattern-based code generation approach presented inthis chapter together with the rewrite rules, we are now able to ad-dress this issue. Our fusion rule (shown in Figure 5.7g) allows to fusetwo patterns into one, thus, avoiding intermediate results. Figure 5.9shows how we can derive a fused version for calculating asum fromthe high-level expression written by the programmer.

160 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 iterate 7 (join � map-local (reduce-seq (+) 0) � split 2) �4 join � toLocal (map-local (map-seq id)) � split 15

�� split 128

Listing 5.8: Expression resembling the first two implementations of parallelreduction presented in Listing 5.1 and Listing 5.2.

these are systematically derived from a single high-level expressionusing the rewrite rules introduced in this section. Therefore, theseimplementations can be generated systematically by an optimizingcompiler. The rules guarantee that all derived expressions are seman-tically equivalent.

Each OpenCL low-level expression presented in this subsection isderived from the high-level expression Equation (5.16) expressing par-allel summation:

vecSum = reduce (+) 0 (5.16)

The formal derivations defining which rules to apply to reach an ex-pression from the high-level expression shown here are presented inAppendix B for all expressions in this subsection.

first pattern-based expression Listing 5.8 shows our firstexpression implementing parallel reduction. This expression closelyresembles the structure of the first two implementations presented inListing 5.1 and Listing 5.2. First the input array is split into chunksof size 128 (line 5) and each work-group processes such a chunk ofdata. 128 corresponds to the work-group size we assumed for ourimplementations in Section 5.1. Inside of a work-group in line 4 eachwork-item first copies a single data item (indicated by split 1) into thelocal memory using the id function nested inside the toLocal pattern toperform a copy. Afterwards, in line 3 the entire work-group performsan iterative reduction where in 7 steps (this equals log

2

(128) follow-ing rule 5.7e) the data is further divided into chunks of two elements(using split 2) which are reduced sequentially by the work-items. Thisiterative process resembles the for-loops from Listing 5.1 and List-ing 5.2 where in every iteration two elements are reduced. Finally,the computed result is copied back to the global memory (line 2).

The first two implementations discussed in Section 5.1 are very sim-ilar and the only difference is which work-item remains active in theparallel reduction tree. Currently, we do not model this subtle dif-ference with our patterns, therefore, we cannot create an expressionwhich distinguishes between these two implementations. This is nota major drawback, because none of the three investigated architec-

rewrite rules code generation

Beispiel: Parallele Summation

kernel void reduce6(global float* g_idata, global float* g_odata, unsigned int n, local volatile float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_group_id(0) * (get_local_size(0)*2) + get_local_id(0); unsigned int gridSize = WG_SIZE * get_num_groups(0); l_data[tid] = 0; while (i < n) { l_data[tid] += g_idata[i]; if (i + WG_SIZE < n) l_data[tid] += g_idata[i+WG_SIZE]; i += gridSize; } barrier(CLK_LOCAL_MEM_FENCE);

if (WG_SIZE >= 256) { if (tid < 128) { l_data[tid] += l_data[tid+128]; } barrier(CLK_LOCAL_MEM_FENCE); } if (WG_SIZE >= 128) { if (tid < 64) { l_data[tid] += l_data[tid+ 64]; } barrier(CLK_LOCAL_MEM_FENCE); } if (tid < 32) { if (WG_SIZE >= 64) { l_data[tid] += l_data[tid+32]; } if (WG_SIZE >= 32) { l_data[tid] += l_data[tid+16]; } if (WG_SIZE >= 16) { l_data[tid] += l_data[tid+ 8]; } if (WG_SIZE >= 8) { l_data[tid] += l_data[tid+ 4]; } if (WG_SIZE >= 4) { l_data[tid] += l_data[tid+ 2]; } if (WG_SIZE >= 2) { l_data[tid] += l_data[tid+ 1]; } } if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 join � map-warp

�

4 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 1 �5 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 2 �6 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 4 �7 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 8 �8 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 16 �9 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 32

10

�� split 64 �

11 join � map-local (reduce-seq (+) 0) � split 2 � reorder-stride 64 �12 join � toLocal (map-local (reduce-seq (+) 0)) �13 split (blockSize/128) � reorder-stride 12814

�� split blockSize

Listing 5.13: Expression resembling the seventh implementation of parallel

160 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 iterate 7 (join � map-local (reduce-seq (+) 0) � split 2) �4 join � toLocal (map-local (map-seq id)) � split 15

�� split 128

Listing 5.8: Expression resembling the first two implementations of parallelreduction presented in Listing 5.1 and Listing 5.2.

these are systematically derived from a single high-level expressionusing the rewrite rules introduced in this section. Therefore, theseimplementations can be generated systematically by an optimizingcompiler. The rules guarantee that all derived expressions are seman-tically equivalent.

Each OpenCL low-level expression presented in this subsection isderived from the high-level expression Equation (5.16) expressing par-allel summation:

vecSum = reduce (+) 0 (5.16)

The formal derivations defining which rules to apply to reach an ex-pression from the high-level expression shown here are presented inAppendix B for all expressions in this subsection.

first pattern-based expression Listing 5.8 shows our firstexpression implementing parallel reduction. This expression closelyresembles the structure of the first two implementations presented inListing 5.1 and Listing 5.2. First the input array is split into chunksof size 128 (line 5) and each work-group processes such a chunk ofdata. 128 corresponds to the work-group size we assumed for ourimplementations in Section 5.1. Inside of a work-group in line 4 eachwork-item first copies a single data item (indicated by split 1) into thelocal memory using the id function nested inside the toLocal pattern toperform a copy. Afterwards, in line 3 the entire work-group performsan iterative reduction where in 7 steps (this equals log

2

(128) follow-ing rule 5.7e) the data is further divided into chunks of two elements(using split 2) which are reduced sequentially by the work-items. Thisiterative process resembles the for-loops from Listing 5.1 and List-ing 5.2 where in every iteration two elements are reduced. Finally,the computed result is copied back to the global memory (line 2).

The first two implementations discussed in Section 5.1 are very sim-ilar and the only difference is which work-item remains active in theparallel reduction tree. Currently, we do not model this subtle dif-ference with our patterns, therefore, we cannot create an expressionwhich distinguishes between these two implementations. This is nota major drawback, because none of the three investigated architec-

rewrite rules code generation

Beispiel: Parallele Summation

mapA,B,I : (A ! B) ! [A]I ! [B]I

zipA,B,I : [A]I ! [B]I ! [A⇥B]I

reduceA,I : ((A⇥A) ! A) ! A ! [A]I ! [A]1

splitA,I : (n : size) ! [A]n⇥I ! [[A]n]I

joinA,I,J : [[A]I ]J ! [A]I⇥J

Algorithmische Primitive

iterateA,I,J : (n : size) ! ((m : size) ! [A]I⇥m ! [A]m)

! [A]In⇥J ! [A]J

asum = reduce (+) 0 �map abs

gemv = � mat xs ys ↵ �.map (+) (

zip (map (scal ↵ � dot xs) mat) (scal � ys) )

dot = � xs ys.(reduce (+) 0 �map (⇤)) (zip xs ys)

scal = � a.map (⇤a)

High-Level Programme

kernel void reduce6(global float* g_idata, global float* g_odata, unsigned int n, local volatile float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_group_id(0) * (get_local_size(0)*2) + get_local_id(0); unsigned int gridSize = WG_SIZE * get_num_groups(0); l_data[tid] = 0; while (i < n) { l_data[tid] += g_idata[i]; if (i + WG_SIZE < n) l_data[tid] += g_idata[i+WG_SIZE]; i += gridSize; } barrier(CLK_LOCAL_MEM_FENCE);

if (WG_SIZE >= 256) { if (tid < 128) { l_data[tid] += l_data[tid+128]; } barrier(CLK_LOCAL_MEM_FENCE); } if (WG_SIZE >= 128) { if (tid < 64) { l_data[tid] += l_data[tid+ 64]; } barrier(CLK_LOCAL_MEM_FENCE); } if (tid < 32) { if (WG_SIZE >= 64) { l_data[tid] += l_data[tid+32]; } if (WG_SIZE >= 32) { l_data[tid] += l_data[tid+16]; } if (WG_SIZE >= 16) { l_data[tid] += l_data[tid+ 8]; } if (WG_SIZE >= 8) { l_data[tid] += l_data[tid+ 4]; } if (WG_SIZE >= 4) { l_data[tid] += l_data[tid+ 2]; } if (WG_SIZE >= 2) { l_data[tid] += l_data[tid+ 1]; } } if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

164 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 join � map-warp

�

4 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 1 �5 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 2 �6 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 4 �7 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 8 �8 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 16 �9 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 32

10

�� split 64 �

11 join � map-local (reduce-seq (+) 0) � split 2 � reorder-stride 64 �12 join � toLocal (map-local (reduce-seq (+) 0)) �13 split (blockSize/128) � reorder-stride 12814

�� split blockSize

Listing 5.13: Expression resembling the seventh implementation of parallelreduction presented in Listing 5.7.

Before we look at how OpenCL code is generated, we discuss oneadditional optimization: fusion of patterns.

5.4.3.3 Systematic Fusion of Patterns

Back in Chapter 4 in Section 4.3 we discussed how the sum of ab-solute values (asum) can be implemented in SkelCL. Two algorithmicskeletons, reduce and map, were composed to express this applicationas shown in Equation (5.17).

asum ~x = reduce (+) 0�

map (| . |) ~x�

(5.17)

where: |a| =

�a if a > 0

-a if a < 0

When evaluating the performance of the SkelCL implementation, weidentified a problem: SkelCL treats each algorithmic skeleton sepa-rately, thus, forcing the map skeleton to write a temporary array backto global memory and then read it again for the next computation,which greatly reduces performance. The temporary array could beavoided, but in the library approach followed by SkelCL it is difficultto implement a generic mechanism for fusing algorithmic skeletons.

By using our pattern-based code generation approach presented inthis chapter together with the rewrite rules, we are now able to ad-dress this issue. Our fusion rule (shown in Figure 5.7g) allows to fusetwo patterns into one, thus, avoiding intermediate results. Figure 5.9shows how we can derive a fused version for calculating asum fromthe high-level expression written by the programmer.

160 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 iterate 7 (join � map-local (reduce-seq (+) 0) � split 2) �4 join � toLocal (map-local (map-seq id)) � split 15

�� split 128

Listing 5.8: Expression resembling the first two implementations of parallelreduction presented in Listing 5.1 and Listing 5.2.

these are systematically derived from a single high-level expressionusing the rewrite rules introduced in this section. Therefore, theseimplementations can be generated systematically by an optimizingcompiler. The rules guarantee that all derived expressions are seman-tically equivalent.

Each OpenCL low-level expression presented in this subsection isderived from the high-level expression Equation (5.16) expressing par-allel summation:

vecSum = reduce (+) 0 (5.16)

The formal derivations defining which rules to apply to reach an ex-pression from the high-level expression shown here are presented inAppendix B for all expressions in this subsection.

first pattern-based expression Listing 5.8 shows our firstexpression implementing parallel reduction. This expression closelyresembles the structure of the first two implementations presented inListing 5.1 and Listing 5.2. First the input array is split into chunksof size 128 (line 5) and each work-group processes such a chunk ofdata. 128 corresponds to the work-group size we assumed for ourimplementations in Section 5.1. Inside of a work-group in line 4 eachwork-item first copies a single data item (indicated by split 1) into thelocal memory using the id function nested inside the toLocal pattern toperform a copy. Afterwards, in line 3 the entire work-group performsan iterative reduction where in 7 steps (this equals log

2

(128) follow-ing rule 5.7e) the data is further divided into chunks of two elements(using split 2) which are reduced sequentially by the work-items. Thisiterative process resembles the for-loops from Listing 5.1 and List-ing 5.2 where in every iteration two elements are reduced. Finally,the computed result is copied back to the global memory (line 2).

The first two implementations discussed in Section 5.1 are very sim-ilar and the only difference is which work-item remains active in theparallel reduction tree. Currently, we do not model this subtle dif-ference with our patterns, therefore, we cannot create an expressionwhich distinguishes between these two implementations. This is nota major drawback, because none of the three investigated architec-

rewrite rules code generation

Beispiel: Parallele Summation

kernel void reduce6(global float* g_idata, global float* g_odata, unsigned int n, local volatile float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_group_id(0) * (get_local_size(0)*2) + get_local_id(0); unsigned int gridSize = WG_SIZE * get_num_groups(0); l_data[tid] = 0; while (i < n) { l_data[tid] += g_idata[i]; if (i + WG_SIZE < n) l_data[tid] += g_idata[i+WG_SIZE]; i += gridSize; } barrier(CLK_LOCAL_MEM_FENCE);

if (WG_SIZE >= 256) { if (tid < 128) { l_data[tid] += l_data[tid+128]; } barrier(CLK_LOCAL_MEM_FENCE); } if (WG_SIZE >= 128) { if (tid < 64) { l_data[tid] += l_data[tid+ 64]; } barrier(CLK_LOCAL_MEM_FENCE); } if (tid < 32) { if (WG_SIZE >= 64) { l_data[tid] += l_data[tid+32]; } if (WG_SIZE >= 32) { l_data[tid] += l_data[tid+16]; } if (WG_SIZE >= 16) { l_data[tid] += l_data[tid+ 8]; } if (WG_SIZE >= 8) { l_data[tid] += l_data[tid+ 4]; } if (WG_SIZE >= 4) { l_data[tid] += l_data[tid+ 2]; } if (WG_SIZE >= 2) { l_data[tid] += l_data[tid+ 1]; } } if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

164 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 join � map-warp

�

4 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 1 �5 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 2 �6 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 4 �7 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 8 �8 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 16 �9 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 32

10

�� split 64 �

11 join � map-local (reduce-seq (+) 0) � split 2 � reorder-stride 64 �12 join � toLocal (map-local (reduce-seq (+) 0)) �13 split (blockSize/128) � reorder-stride 12814

�� split blockSize

Listing 5.13: Expression resembling the seventh implementation of parallelreduction presented in Listing 5.7.

Before we look at how OpenCL code is generated, we discuss oneadditional optimization: fusion of patterns.

5.4.3.3 Systematic Fusion of Patterns

Back in Chapter 4 in Section 4.3 we discussed how the sum of ab-solute values (asum) can be implemented in SkelCL. Two algorithmicskeletons, reduce and map, were composed to express this applicationas shown in Equation (5.17).

asum ~x = reduce (+) 0�

map (| . |) ~x�

(5.17)

where: |a| =

�a if a > 0

-a if a < 0

When evaluating the performance of the SkelCL implementation, weidentified a problem: SkelCL treats each algorithmic skeleton sepa-rately, thus, forcing the map skeleton to write a temporary array backto global memory and then read it again for the next computation,which greatly reduces performance. The temporary array could beavoided, but in the library approach followed by SkelCL it is difficultto implement a generic mechanism for fusing algorithmic skeletons.

By using our pattern-based code generation approach presented inthis chapter together with the rewrite rules, we are now able to ad-dress this issue. Our fusion rule (shown in Figure 5.7g) allows to fusetwo patterns into one, thus, avoiding intermediate results. Figure 5.9shows how we can derive a fused version for calculating asum fromthe high-level expression written by the programmer.

vecSum = reduce (+) 0

rewrite rules code generation

Beispiel: Parallele Summation

map f �map g ! map (f � g)Map Zusammenschluss:

reduce f z ! reduce f z � reducePart f z

reducePart f z ! iterate n (reducePart f z)

reducePart f z ! reducePart f z � reorderreducePart f z ! join �map (reducePart f z) � split n

Reduktionsregeln:

map f ! join �map (map f) � split nSplit-Join Zerlegung:

Algorithmische Transformationsregeln

• Transformationsregeln sind semantikerhaltend

• Drücken Auswahl bei der algorithmische Implementierungen aus

OpenCL Primitive

Primitive OpenCL Konzept

mapGlobal Work-items

mapWorkgroup / mapLocal Work-groups

mapSeq / reduceSeq Sequentielle Implementierungen

toLocal / toGlobal Speicherbereiche

mapVec / splitVec / joinVec Vektorisierung

map f ! mapWorkgroup f | mapLocal f | mapGlobal f | mapSeq f

Map:

• Drücken hardware-spezifische Optimierungen aus

mapLocal f ! toGlobal (mapLocal f)mapLocal f ! toLocal (mapLocal f)

Lokaler/ Globaler Speicher:

map f ! joinVec �map (mapVec f) � splitVec nVektorisierung:

reduceSeq f z �mapSeq g ! reduceSeq (� (acc, x). f (acc, g x)) zMap-Reduktion Zusammenschluss:

OpenCL Transformationsregeln

kernel void reduce6(global float* g_idata, global float* g_odata, unsigned int n, local volatile float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_group_id(0) * (get_local_size(0)*2) + get_local_id(0); unsigned int gridSize = WG_SIZE * get_num_groups(0); l_data[tid] = 0; while (i < n) { l_data[tid] += g_idata[i]; if (i + WG_SIZE < n) l_data[tid] += g_idata[i+WG_SIZE]; i += gridSize; } barrier(CLK_LOCAL_MEM_FENCE);

if (WG_SIZE >= 256) { if (tid < 128) { l_data[tid] += l_data[tid+128]; } barrier(CLK_LOCAL_MEM_FENCE); } if (WG_SIZE >= 128) { if (tid < 64) { l_data[tid] += l_data[tid+ 64]; } barrier(CLK_LOCAL_MEM_FENCE); } if (tid < 32) { if (WG_SIZE >= 64) { l_data[tid] += l_data[tid+32]; } if (WG_SIZE >= 32) { l_data[tid] += l_data[tid+16]; } if (WG_SIZE >= 16) { l_data[tid] += l_data[tid+ 8]; } if (WG_SIZE >= 8) { l_data[tid] += l_data[tid+ 4]; } if (WG_SIZE >= 4) { l_data[tid] += l_data[tid+ 2]; } if (WG_SIZE >= 2) { l_data[tid] += l_data[tid+ 1]; } } if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

164 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 join � map-warp

�

4 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 1 �5 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 2 �6 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 4 �7 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 8 �8 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 16 �9 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 32

10

�� split 64 �

11 join � map-local (reduce-seq (+) 0) � split 2 � reorder-stride 64 �12 join � toLocal (map-local (reduce-seq (+) 0)) �13 split (blockSize/128) � reorder-stride 12814

�� split blockSize

Listing 5.13: Expression resembling the seventh implementation of parallelreduction presented in Listing 5.7.

Before we look at how OpenCL code is generated, we discuss oneadditional optimization: fusion of patterns.

5.4.3.3 Systematic Fusion of Patterns

Back in Chapter 4 in Section 4.3 we discussed how the sum of ab-solute values (asum) can be implemented in SkelCL. Two algorithmicskeletons, reduce and map, were composed to express this applicationas shown in Equation (5.17).

asum ~x = reduce (+) 0�

map (| . |) ~x�

(5.17)

where: |a| =

�a if a > 0

-a if a < 0

When evaluating the performance of the SkelCL implementation, weidentified a problem: SkelCL treats each algorithmic skeleton sepa-rately, thus, forcing the map skeleton to write a temporary array backto global memory and then read it again for the next computation,which greatly reduces performance. The temporary array could beavoided, but in the library approach followed by SkelCL it is difficultto implement a generic mechanism for fusing algorithmic skeletons.

By using our pattern-based code generation approach presented inthis chapter together with the rewrite rules, we are now able to ad-dress this issue. Our fusion rule (shown in Figure 5.7g) allows to fusetwo patterns into one, thus, avoiding intermediate results. Figure 5.9shows how we can derive a fused version for calculating asum fromthe high-level expression written by the programmer.

160 code generation using patterns

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 iterate 7 (join � map-local (reduce-seq (+) 0) � split 2) �4 join � toLocal (map-local (map-seq id)) � split 15

�� split 128

Listing 5.8: Expression resembling the first two implementations of parallelreduction presented in Listing 5.1 and Listing 5.2.

these are systematically derived from a single high-level expressionusing the rewrite rules introduced in this section. Therefore, theseimplementations can be generated systematically by an optimizingcompiler. The rules guarantee that all derived expressions are seman-tically equivalent.

Each OpenCL low-level expression presented in this subsection isderived from the high-level expression Equation (5.16) expressing par-allel summation:

vecSum = reduce (+) 0 (5.16)

The formal derivations defining which rules to apply to reach an ex-pression from the high-level expression shown here are presented inAppendix B for all expressions in this subsection.

first pattern-based expression Listing 5.8 shows our firstexpression implementing parallel reduction. This expression closelyresembles the structure of the first two implementations presented inListing 5.1 and Listing 5.2. First the input array is split into chunksof size 128 (line 5) and each work-group processes such a chunk ofdata. 128 corresponds to the work-group size we assumed for ourimplementations in Section 5.1. Inside of a work-group in line 4 eachwork-item first copies a single data item (indicated by split 1) into thelocal memory using the id function nested inside the toLocal pattern toperform a copy. Afterwards, in line 3 the entire work-group performsan iterative reduction where in 7 steps (this equals log

2

(128) follow-ing rule 5.7e) the data is further divided into chunks of two elements(using split 2) which are reduced sequentially by the work-items. Thisiterative process resembles the for-loops from Listing 5.1 and List-ing 5.2 where in every iteration two elements are reduced. Finally,the computed result is copied back to the global memory (line 2).

The first two implementations discussed in Section 5.1 are very sim-ilar and the only difference is which work-item remains active in theparallel reduction tree. Currently, we do not model this subtle dif-ference with our patterns, therefore, we cannot create an expressionwhich distinguishes between these two implementations. This is nota major drawback, because none of the three investigated architec-

rewrite rules code generation

Beispiel: Parallele Summation

kernel void reduce6(global float* g_idata, global float* g_odata, unsigned int n, local volatile float* l_data) { unsigned int tid = get_local_id(0); unsigned int i = get_group_id(0) * (get_local_size(0)*2) + get_local_id(0); unsigned int gridSize = WG_SIZE * get_num_groups(0); l_data[tid] = 0; while (i < n) { l_data[tid] += g_idata[i]; if (i + WG_SIZE < n) l_data[tid] += g_idata[i+WG_SIZE]; i += gridSize; } barrier(CLK_LOCAL_MEM_FENCE);

if (WG_SIZE >= 256) { if (tid < 128) { l_data[tid] += l_data[tid+128]; } barrier(CLK_LOCAL_MEM_FENCE); } if (WG_SIZE >= 128) { if (tid < 64) { l_data[tid] += l_data[tid+ 64]; } barrier(CLK_LOCAL_MEM_FENCE); } if (tid < 32) { if (WG_SIZE >= 64) { l_data[tid] += l_data[tid+32]; } if (WG_SIZE >= 32) { l_data[tid] += l_data[tid+16]; } if (WG_SIZE >= 16) { l_data[tid] += l_data[tid+ 8]; } if (WG_SIZE >= 8) { l_data[tid] += l_data[tid+ 4]; } if (WG_SIZE >= 4) { l_data[tid] += l_data[tid+ 2]; } if (WG_SIZE >= 2) { l_data[tid] += l_data[tid+ 1]; } } if (tid == 0) g_odata[get_group_id(0)] = l_data[0]; }

1 vecSum = reduce � join � map-workgroup�

2 join � toGlobal (map-local (map-seq id)) � split 1 �3 join � map-warp

�

4 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 1 �5 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 2 �6 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 4 �7 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 8 �8 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 16 �9 join � map-lane (reduce-seq (+) 0) � split 2 � reorder-stride 32

10

�� split 64 �

11 join � map-local (reduce-seq (+) 0) � split 2 � reorder-stride 64 �12 join � toLocal (map-local (reduce-seq (+) 0)) �13 split (blockSize/128) � reorder-stride 12814

�� split blockSize

Listing 5.13: Expression resembling the seventh implementation of parallel

vecSum = reduce (+) 0

rewrite rules code generation

Beispiel: Parallele Summation

mapGlobal f xs

for (int g_id = get_global_id(0); g_id < n; g_id += get_global_size(0)) { output[g_id] = f(xs[g_id]); }

reduceSeq f z xs

T acc = z; for (int i = 0; i < n; ++i) { acc = f(acc, xs[i]); }

......

Muster basierte OpenCL Codegenerierung

• Generiere OpenCL Code für jedes OpenCL Primitiv

reduce (+) 0

reduce (+) 0 ○ reducePart (+) 0

reduce (+) 0 ○ reducePart (+) 0 ○ reorder

reduce (+) 0 ○ join ○ map (reducePart (+) 0) ○ split n

reduce (+) 0 ○ iterate n (reducePart (+) 0)

…

…

…

Transformationsregeln definiereneinen Suchraum gültiger Implementierungen

reduce (+) 0

reduce (+) 0 ○ reducePart (+) 0

reduce (+) 0 ○ reducePart (+) 0 ○ reorder

reduce (+) 0 ○ join ○ map (reducePart (+) 0) ○ split n

reduce (+) 0 ○ iterate n (reducePart (+) 0)

…

…

…

Transformationsregeln definiereneinen Suchraum gültiger Implementierungen

reduce (+) 0

reduce (+) 0 ○ reducePart (+) 0

reduce (+) 0 ○ reducePart (+) 0 ○ reorder

reduce (+) 0 ○ join ○ map (reducePart (+) 0) ○ split n

reduce (+) 0 ○ iterate n (reducePart (+) 0)

…

…

…

Transformationsregeln definiereneinen Suchraum gültiger Implementierungen

reduce (+) 0

reduce (+) 0 ○ reducePart (+) 0

reduce (+) 0 ○ reducePart (+) 0 ○ reorder

reduce (+) 0 ○ join ○ map (reducePart (+) 0) ○ split n

reduce (+) 0 ○ iterate n (reducePart (+) 0)

…

…

…

Transformationsregeln definiereneinen Suchraum gültiger Implementierungen

reduce (+) 0

reduce (+) 0 ○ reducePart (+) 0

reduce (+) 0 ○ reducePart (+) 0 ○ reorder

reduce (+) 0 ○ join ○ map (reducePart (+) 0) ○ split n

reduce (+) 0 ○ iterate n (reducePart (+) 0)

…

…

…

• Vollautomatische Suche nach guten Implementierungen möglich! (Eine einfache Suchstrategie ist in der Dissertation beschrieben)

Transformationsregeln definiereneinen Suchraum gültiger Implementierungen

0

1

2

3

420 8.5 4.5

small large small large small large small largescal asum dot gemv Black

Scholes MD

Sp

ee

du

pNvidia GPU AMD GPU Intel CPU

Figure 14: Performance of our approach relative to a portableOpenCL reference implementation (clBLAS).

9. ResultsWe now evaluate our approach compared to a reference OpenCLimplementations of our benchmarks on all platforms. Furthermore,we compare the BLAS routines against platform-specific highlytuned implementations.

9.1 Comparison vs. Portable ImplementationFirst, we show how our approach performs across three platforms.We use the clBLAS OpenCL implementations written by AMDas our baseline for this evaluation since it is inherently portableacross all different platforms. Figure 14 shows the performance ofour approach relative to clBLAS. As can be seen, we achieve betterperformance than clBLAS on most platforms and benchmarks. Thespeedups are the highest for the CPU, with up to 20⇥ for the asumbenchmark with a small input size. The reason is that clBLAS waswritten and tuned specifically for an AMD GPU which usuallyexhibits a larger number of parallel processing units. As we saw inSection 6, our systematically derived expression for this benchmarkis specifically tuned for the CPU by avoiding creating too muchparallelism, which is what gives us such large speedup.

Figure 14 also shows the results we obtain relative to the NvidiaSDK BlackScholes and SHOC molecular dynamics MD bench-mark. For BlackScholes, we see that our approach is on par withthe performance of the Nvidia implementation on both GPUs. Onthe CPU, we actually achieve a 2.2⇥ speedup due to the fact thatthe Nvidia implementation is tuned for GPUs while our implemen-tation generates different code for the CPU. For MD, we are on parwith the OpenCL implementation on all platforms.

9.2 Comparison vs. Highly-tuned ImplementationsWe compare our approach with a state of the art implementationfor each platform. For Nvidia, we pick the highly tuned CUBLASimplementation of BLAS written by Nvidia. For the AMD GPU,we use the same clBLAS implementation as before given that ithas been written and tuned specifically for AMD GPUs. Finally, forthe CPU we use the Math Kernel Library (MKL) implementationof BLAS written by Intel, which is known for its high performance.

Similar to the high performance libraries our approach resultsin device-specific OpenCL code with implementation parameterstuned for specific data sizes. In contrast, existing library approachesare based on device-specific manually optimized implementationswhereas our approach systematically and automatically generatesthese specialized versions.

Figure 15a shows that we actually match the performance ofCUBLAS for scal, asum and dot on the Nvidia GPU. For gemv weoutperform CUBLAS on the small size by 20% while we are within5% for the large input size. Given that CUBLAS is a proprietary

library highly tuned for Nvidia GPUs, these results show that ourtechnique is able to achieve high performance.

On the AMD GPU, we are surprisingly up to 4.5⇥ faster thanthe clBLAS implementation on gemv small input size as shownin Figure 15b. The reason for this is found in the way clBLAS isimplemented; clBLAS performs automatic code generation usingfixed templates. In contrast to our approach, they only generateone implementation since they do not explore different templatecompositions.

For the Intel CPU (Figure 15c), our approach beats MKL for onebenchmark and matches the performance of MKL on most of theother three benchmarks. For the small input sizes for the scal anddot benchmarks we are within 13% and 30% respectively. For thelarger input sizes, we are on par with MKL for both benchmarks.The asum implementation in the MKL does not use thread levelparallelism, where our implementation does and, thus, achieves aspeedup of up to 1.78 on the larger input size.

This section has shown that our approach generates perfor-mance portable code which is competitive with highly-tuned plat-form specific implementations. Our systematic approach is genericand generates optimized kernels for different devices or datasizes. Therefore, our results suggest that high performance canbe achieved for different input sizes and for other benchmarks ex-pressible with our primitives.

10. Related WorkAlgorithmic Patterns Algorithmic patterns (or algorithmic skele-tons [11]) have been around for more than two decades. Earlywork already discussed algorithmic skeletons in the context ofperformance portability [16]. Patterns are parts of popular frame-works such as Map-Reduce [18] from Google. Current pattern-based libraries for platforms ranging from cluster systems [37] toGPUs [41] have been proposed with recent extension to irregular al-gorithms [20]. Lee et al., [28] discuss how nested parallel patternscan be mapped efficiently to GPUs. Compared to our approach,most prior work relies on hardware-specific implementations toachieve high performance. Conversely, we systematically generateimplementations using fine-grain OpenCL patterns combined withour rule rewriting system.

Algebra of Programming Bird and Meertens, amongst others,developed formalisms for algebraic reasoning about functional pro-grams in the 1980s [5]. Our rewrite rules are in the same spirit andmany of our rules are similar to equational rules presented by Bird,Meertens, and others. Skillicorn [38] described the application ofthe algebraic approach for parallel computing. He argued that itleads to architecture-independent parallel programming — whichwe call performance portability in this paper. Our work can be seenas an application of the algebraic approach to the generation of ef-ficient code for modern parallel processors.

Functional Approaches for GPU Code Generation Accelerateis a functional domain specific language embedded into Haskell tosupport GPU acceleration [9, 30]. Obsidian [42] and Harlan [24]are earlier projects with similar goals. Obsidian exposes more de-tails of the underlying GPU hardware to the programmer. Harlanis a declarative programming language compiled to GPU code.Bergstrom and Reppy [4] compile NESL, which is a first-order di-alect of ML supporting nested data-parallelism, to GPU code. Re-cently, Nvidia introduced NOVA [12], a new functional languagetargeted at code generation for GPUs, and Copperhead [7], a dataparallel language embedded in Python. HiDP [46] is a hierarchicaldata parallel language which maps computations to OpenCL. Allthese projects rely on code analysis or hand-tuned versions of high-level algorithmic patterns. In contrast, our approach uses rewrite

Evaluation — Geschwindigkeitgegenüber einer funktional portablen Implementierung

Bis zu 20x Speedup gegenüber der funktional portablen clBLAS Implementierung

gegenüber Hardware spezifischen Implementierungen

• Automatisch generierter Code vs. handoptimierten Code • Konkurrenzfähige Ergebnisse vs. hochoptimierte Implementierungen • Bis zu 4.5x Speedup für gemv auf der AMD GPU

0

1

2

small large small large small large small large

scal asum dot gemv

Sp

ee

du

p o

ver

CU

BL

AS

CUBLAS Generated

(a) Nvidia GPU

0

1

24.5 3.1

small large small large small large small large

scal asum dot gemv

Sp

ee

du

p o

ver

clB

LA

S

clBLAS Generated

(b) AMD GPU

0

1

2

small large small large small large small large

scal asum dot gemv

Sp

ee

du

p o

ver

MK

L

MKL Generated

(c) Intel CPU

Figure 15: Performance comparison with state of the art platform-specific libraries; CUBLAS for Nvidia, clBLAS for AMD, MKL for Intel.Our approach matches the performance on all three platforms and outperforms clBLAS in some cases.

rules and low-level hardware patterns to produce high-performancecode in a portable way.

Halide [35] is a domain specific approach that targets image pro-cessing pipelines. It separates the algorithmic description from op-timization decisions. Our work is domain agnostic and takes a dif-ferent approach. We systematically describe hardware paradigmsas functional patterns instead of encoding specific optimizationswhich might not apply to future hardware generations.

Rewrite-rules for Optimizations Rewrite rules have been usedas a way to automate the optimization process of functional pro-grams [26]. Recently, rewriting has been applied to HPC appli-cations [32] as well, where the rewrite process uses user annota-tions on imperative code. Similar to us, Spiral [34] uses rewriterules to optimize signal processing programs and was more recentlyadapted to linear algebra [39]. In contrast, our rules and OpenCLhardware patterns are expressed at a much finer level, allowing forhighly specialized and optimized code generation.

Automatic Code Generation for GPUs A large body of workhas explored how to generate high performance code for GPUs.Dataflow programming models such as StreamIt [43] or Liq-uidMetal [19] have been used to produce GPU code. Directivebased approaches such as OpenMP to CUDA [29], OpenACC toOpenCL [36], or hiCUDA [22] compile sequential C code for theGPU. X10, a language for high performance computing, can alsobe used to program GPUs [14]. However, this remains low-levelsince the programmer has to express the same low-level operationsfound in CUDA or OpenCL. Recently, researchers have lookedat generating efficient GPU code for loops using the polyhedralframework [44]. Delite [6, 8], a system that enables the creationof domain-specific languages, can also target multicore CPUs orGPUs. Unfortunately, all these approaches do not provide full per-formance portability since the mapping of the application assumesa fixed platform and the optimizations and implementations aretargeted at a specific device.

Finally, Petabricks [3] takes a different approach by lettingthe programmer specify different algorithms implementations. Thecompiler and runtime choose the most suitable one based on anadaptive mechanism and produces OpenCL code [33]. Comparedto our work, this technique relies on static analysis to optimizecode. Our code generator does not perform any analysis sinceoptimization happens at a higher level within our rewrite rules.

11. ConclusionIn this paper, we have presented a novel approach based on rewriterules to represent algorithmic principles as well as low-levelhardware-specific optimization. We have shown how these rulescan be systematically applied to transform a high-level expressioninto high-performance device-specific implementations. We pre-sented a formalism, which we use to prove the correctness of thepresented rewrite rules. Our approach results in a clear separationof concerns between high-level algorithmic concepts and low-levelhardware optimizations which pave the way for fully automatedhigh performance code generation.

To demonstrate our approach in practice, we have developedOpenCL-specific primitives and rules together with an OpenCLcode generator. The design of the code generator is straightfor-ward given that all optimizations decisions are made with the rulesand no complex analysis is needed. We achieve performance on parwith highly tuned platform-specific BLAS libraries on three differ-ent processors. For some benchmarks such as matrix vector multi-plication we even reach a speedup of up to 4.5. We also show thatour technique can be applied to more complex applications such asBlackScholes or for molecular dynamics simulation.

AcknowledgmentsThis work was supported by a HiPEAC collaboration grant, EPSRC(grant number EP/K034413/1), the Royal Academy of Engineer-ing, Google and Oracle. We are grateful to the anonymous review-ers who helped to substantially improve the quality of the paper.We would like to thank Sergei Gorlatch for his active support of theHiPEAC collaboration and the following people for their involve-ment in the discussions on formalization: Robert Atkey, James Ch-eney, Stefan Fehrenbach, Adam Harries, Shayan Najd, and PhilipWadler.

References[1] AMD Accelerated Parallel Processing OpenCL Programming Guide.

AMD, 2013.

[2] C. Andreetta, V. Begot, J. Berthold, M. Elsman, T. Henriksen, M.-B. Nordfang, and C. Oancea. A financial benchmark for GPGPUcompilation. Technical Report no 2015/02, University of Copenhagen,2015. Extended version of CPC’15 paper.

[3] J. Ansel, C. Chan, Y. L. Wong, M. Olszewski, Q. Zhao, A. Edelman,and S. Amarasinghe. PetaBricks: a language and compiler for algo-rithmic choice. PLDI. ACM, 2009.

Evaluation — Geschwindigkeit

Zusammenfassung

• Um die Herausforderung der Programmierbarkeit zu adressieren:

• Ein neuer Ansatz zur Programmierung von Systemen mit mehreren GPUs

• Zwei neue formell definierte und implementierte algorithmische Skelette

• Um die Herausforderung der Performance-Portabilität zu adressieren:

• Ein formelles System zur Transformation muster-basierter Programme

• Ein Codegenerator der Performance-Portabilität erreicht

asum

I

: [float]I

! [float]1asum

I⇥J

= reducefloat,I⇥J

(+) 0 � map abs

6d! reducefloat,J (+) 0 � reducePartfloat,I (+) 0 J � map abs (1)6d! reduce (+) 0 � join � map (reducePart (+) 0 1) � splitfloat,J I � map abs (2)6c! reduce (+) 0 � join � map (reducePart (+) 0 1) � split I � join � map (map abs) � split I (3)6e! reduce (+) 0 � join � map (reducePart (+) 0 1) � map (map abs) � split I (4)6f! reduce (+) 0 � join � map (reducePart (+) 0 1 � map abs) � split I (5)7a! reduce (+) 0 � join � map (reducePart (+) 0 1 � mapSeq abs) � split I (6)

6d&7b! reduce (+) 0 � join � map (reduceSeq (+) 0 � mapSeq abs) � split I (7)6f! reduce (+) 0 � join � map (reduceSeq (�(acc, a).acc + (abs a)) 0) � split I (8)

Figure 10: Derivation of a fused parallel implementation of absolute sum.

(a) NvidiaGPU

�x.(reduceSeq � join � join � mapWorkgroup (

toGlobal�mapLocal (reduceSeq (�(a, b). a+ (abs b)) 0)

�� reorderStride 2048

) � split 128 � split 2048) x

(b) AMDGPU

�x.(reduceSeq � join � joinVec � join � mapWorkgroup (

mapLocal (reduceSeq (mapVec 2 (�(a, b). a+ (abs b))) 0 � reorderStride 2048

) � split 128 � splitVec 2 � split 4096) x

(c) IntelCPU

�x.(reduceSeq � join � mapWorkgroup (join � joinVec � mapLocal (reduceSeq (mapVec 4 (�(a, b). a+ (abs b))) 0

) � splitVec 4 � split 32768) � split 32768) x

Figure 11: Low-level expressions performing the sum of absolute values. These expressions are automatically derived by our system fromthe high-level expression asum = reduce (+) 0 � map abs .

●●●●

●●

●

●

●●●●●

●

●

●

●

●●●●●●

●

●

●

●

●●

●

●●

●

●

●

●

●●

●●

●

●

●●

●

●

●

●●

●

●●

●

●●●●

●●●

●

●

●

●

●

●●

●●

0 10 20 30 40 50 60 70

020

4060

8012

0

Number of evaluated expressions

Abso

lute

per

form

ance

in G

B/s

(a) Nvidia GPU

●

●

●●

●●●●●

●●●

●

●●●

●

●●

●●

●

●●●●●●●

●●

●●

●

●●●

●●●

●

●

●

●●●

●

●

●

●

●

●

●●

●

●

●

●

●

●●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

0 20 40 60 80

050

100

150

200

Number of evaluated expressions

Abso

lute

per

form

ance

in G

B/s

(b) AMD GPU

●●●●●●●

●

●●

●●

●●

●●●

●

●●●

●●

●●●●●●

●●

●●●●

●

●●●●

●●●●●

●●●

●

●●

●●●●

●●

●

●

●

●●●●●●

●●●●

●●

●●●●●

●●●

●

●

●●●

●

●

●●●●●

●

●●

●

●

●

●

●●

●

●

●●●●●

●

●

●●

●●●

●

●

●●●●

●

●●

●

●

●●

●

0 20 40 60 80 100 120

05

1015

Number of evaluated expressions

Abso

lute

per

form

ance

in G

B/s

(c) Intel CPU

Figure 12: Search efficiency. Each point shows the performance of the OpenCL code generated from a tested expression. The horizontalpartitioning visualized using vertical bars represents the number of fixed derivations in the search tree. The red line connects the fastestexpressions found so far.

7. BenchmarksWe now discuss how applications can be represented as expressionscomposed of our high-level algorithmic primitives using a set ofeasy to understand benchmarks from the fields of linear algebra,mathematical finance, and physics.

7.1 Linear Algebra KernelsWe choose linear algebra kernels as our first set of benchmarks,because they are well known, easy to understand, and used asbuilding blocks in many other applications. Figure 13 shows howwe express vector scaling, sum of absolute values, dot productof two vectors and matrix vector multiplication using our high-

asum = reduce (+) 0 �map abs

Ergebnisse der SucheAutomatisch Gefundene Ausdrücke

Gesucht für: Nvidia GTX 480 GPU, AMD Radeon HD 7970 GPU, Intel Xeon E5530 CPU

Effizienz der Suche

asum

I

: [float]I

! [float]1asum

I⇥J

= reducefloat,I⇥J

(+) 0 � map abs

6d! reducefloat,J (+) 0 � reducePartfloat,I (+) 0 J � map abs (1)6d! reduce (+) 0 � join � map (reducePart (+) 0 1) � splitfloat,J I � map abs (2)6c! reduce (+) 0 � join � map (reducePart (+) 0 1) � split I � join � map (map abs) � split I (3)6e! reduce (+) 0 � join � map (reducePart (+) 0 1) � map (map abs) � split I (4)6f! reduce (+) 0 � join � map (reducePart (+) 0 1 � map abs) � split I (5)7a! reduce (+) 0 � join � map (reducePart (+) 0 1 � mapSeq abs) � split I (6)

6d&7b! reduce (+) 0 � join � map (reduceSeq (+) 0 � mapSeq abs) � split I (7)6f! reduce (+) 0 � join � map (reduceSeq (�(acc, a).acc + (abs a)) 0) � split I (8)

Figure 10: Derivation of a fused parallel implementation of absolute sum.

(a) NvidiaGPU

�x.(reduceSeq � join � join � mapWorkgroup (

toGlobal�mapLocal (reduceSeq (�(a, b). a+ (abs b)) 0)

�� reorderStride 2048

) � split 128 � split 2048) x

(b) AMDGPU

�x.(reduceSeq � join � joinVec � join � mapWorkgroup (

mapLocal (reduceSeq (mapVec 2 (�(a, b). a+ (abs b))) 0 � reorderStride 2048

) � split 128 � splitVec 2 � split 4096) x

(c) IntelCPU

�x.(reduceSeq � join � mapWorkgroup (join � joinVec � mapLocal (reduceSeq (mapVec 4 (�(a, b). a+ (abs b))) 0

) � splitVec 4 � split 32768) � split 32768) x

Figure 11: Low-level expressions performing the sum of absolute values. These expressions are automatically derived by our system fromthe high-level expression asum = reduce (+) 0 � map abs .

●●●●

●●

●

●

●●●●●

●

●

●

●

●●●●●●

●

●

●

●

●●

●

●●

●

●

●

●

●●

●●

●

●

●●

●

●

●

●●

●

●●

●

●●●●

●●●

●

●

●

●

●

●●

●●

0 10 20 30 40 50 60 70

020

4060

8012

0

Number of evaluated expressions

Abso

lute

per

form

ance

in G

B/s

(a) Nvidia GPU

●

●

●●

●●●●●

●●●

●

●●●

●

●●

●●

●

●●●●●●●

●●

●●

●

●●●

●●●

●

●

●

●●●

●

●

●

●

●

●

●●

●

●

●

●

●

●●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

●

0 20 40 60 80

050

100

150

200

Number of evaluated expressions

Abso

lute

per

form

ance

in G

B/s

(b) AMD GPU

●●●●●●●

●

●●

●●

●●

●●●

●

●●●

●●

●●●●●●

●●

●●●●

●

●●●●

●●●●●

●●●

●

●●

●●●●

●●

●

●

●

●●●●●●

●●●●

●●

●●●●●

●●●

●

●

●●●

●

●

●●●●●

●

●●

●

●

●

●

●●

●

●

●●●●●

●

●

●●

●●●

●

●

●●●●

●

●●

●

●

●●

●

0 20 40 60 80 100 120

05

1015

Number of evaluated expressions

Abso

lute

per

form

ance

in G

B/s

(c) Intel CPU

Figure 12: Search efficiency. Each point shows the performance of the OpenCL code generated from a tested expression. The horizontalpartitioning visualized using vertical bars represents the number of fixed derivations in the search tree. The red line connects the fastestexpressions found so far.

7. BenchmarksWe now discuss how applications can be represented as expressionscomposed of our high-level algorithmic primitives using a set ofeasy to understand benchmarks from the fields of linear algebra,mathematical finance, and physics.

7.1 Linear Algebra KernelsWe choose linear algebra kernels as our first set of benchmarks,because they are well known, easy to understand, and used asbuilding blocks in many other applications. Figure 13 shows howwe express vector scaling, sum of absolute values, dot productof two vectors and matrix vector multiplication using our high-

• Die Suche hat auf jeder Platform weniger als 1 Stunde gedauert

• Durchschnittliche Zeit zur Ausführung eines Kandidaten weniger als 1/2 Sekunde

Ergebnisse der Suche

• Optimieren in OpenCL ist kompliziert • Verständnis für die Zielarchitektur benötigt

• Veränderungen im Program nicht offensichtlich