Aprofundando Aprendizado 06 Pipeline

Transcript of Aprofundando Aprendizado 06 Pipeline

Aprofundando o aprendizadoCompreendendo pipelines por meio de desenhos

6.7 [5] <§6.2> Na página 298, mostramos um exemplo com a seguinte seqüência de código:

lw $10, 20($1)sub $11, $2, $3

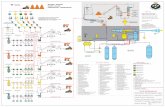

As Figuras 6.19 e 6.20 mostraram os diagramas de pipeline com múltiplos ciclos de clock paraessa seqüência de duas instruções, executando por 6 ciclos de clock. As Figuras de 6.14.1 a 6.14.3mostram os diagramas de pipeline de ciclo único de clock correspondentes para essas duas instru-ções. Observe que a ordem das instruções difere entre esses dois tipos de diagramas: a instrução maisnova está na parte inferior direita do diagrama de pipeline com múltiplos ciclos de clock e está à es-querda no diagrama de pipeline com ciclo único de clock.

Nos três exercícios a seguir, use a seguinte seqüência de código:

add $4, $2, $3sw $5, 4($2)

Para a seqüência de código anterior, desenhe o diagrama de pipeline com múltiplos ciclos declock usando o formato mostrado na Figura 6.19.

6.8 [5] <§6.2> Para a seqüência de código no Exercício 6.6, desenhe o diagrama de pipeline commúltiplos ciclos de clock usando o formato mostrado na Figura 6.20.

6.9 [15] <§6.2> Para a seqüência de código anterior, mostre o pipeline por 6 ciclos de clock usandoos diagramas de ciclo único de clock, como nas Figuras de 6.14.1 a 6.14.3. A Figura 6.14.4 possuium diagrama de pipeline com ciclo único de clock em branco, que pode ser reproduzido para facilitarsua tarefa!

Aprofundando o aprendizado 6-14-1

6-14-2 Aprofundando o aprendizado ELSEVIER

Memória deinstrução

Endereço

4

3232

Inst

ruct

ion

Add

Add

PC

Registradores

Readdata 1

Readdata 2

Readregister 1

Readregister 2

1616 Exten-são desinal

WrWriteiteregisterregister

WrWriteitedatadata

Memória deinstrução

Endereço

4

3232

Add AddAddresultresult

Shiftleft 2

Shiftleft 2

Inst

rIn

stru

ctio

nuc

tion

PC

WrWriteitedatadata

Registradores

ReadReaddata 1data 1

ReadReaddata 2data 2

ReadReadregister 1register 1

ReadReadregister 2register 2

1616

WrWriteiteregisterregister

WrWriteitedatadata

ReadReaddatadata

ALUALUresultresult

ALUZeroZero

Add AddAddresultresult

ALUALUresultresult

ALUZeroZero

Busca de instrBusca de instruçãoução

EndereçoEndereço

Memória dedados

WrWriteitedatadata

ReadReaddatadata

AddressAddress

Memória dedados

Mux

00

11

Mux

0

1

Mux

0

1

Mux

11

00

Mux

11

00

Mux

00

11

IF/ID EX/MEMEX/MEM MEM/WBMEM/WBID/EX

DecodificaçãoDecodificaçãode instrde instruçãoução

lw $10, 20($1)Busca de instrBusca de instruçãoução

sub $11, $2, $3

IF/ID EX/MEMEX/MEMID/EXID/EX

lw $10, 20($1)

Clock 1

Clock 2

MEM/WBMEM/WB

Exten-são desinal

FIGURA 6.14.1 Diagramas de pipeline com ciclo único para os ciclos de clock 1 (diagrama superior) e 2(diagrama inferior). Esse estilo de representação de pipeline é um instantâneo de cada instrução executando durante1 ciclo de clock. Nosso exemplo tem tudo menos duas instruções, de modo que no máximo dois estágios são identificadosem cada ciclo de clock; normalmente, todos os cinco estágios estão ocupados. As partes destacadas do caminho de dadosestão ativas nesse ciclo de clock. O load é buscado no ciclo de clock 1 e decodificado no ciclo de clock 2, com o subtractbuscado no segundo ciclo de clock. Para tornar as figuras mais fáceis de entender, os outros estágios do pipeline estão vazi-os, mas normalmente existe uma instrução em cada estágio do pipeline.

Aprofundando o aprendizado 6-14-3

Memória deinstrução

EndereçoEndereço

4

3232

Inst

rIn

stru

ctio

nuc

tion

IF/IDIF/ID EX/MEM MEM/WB

Add

Add

LerLerdados 1dados 1

LerLerdados 2dados 2

ReadReadregisterregister 11

ReadReadregisterregister 22

1616

WrWriteiteregisterregister

EscreEscrevvererdadosdados

ID/EX

MemórMemóriaialw $10, 20($1)

ExExecuçãoecuçãosub $11, $2, $3

EndereçoEndereço

4

3232

Add Addresult

Shiftleft 2

Add AddAddresultresult

Shiftleft 2

Inst

ruct

ion

IF/ID EX/MEM MEM/WB

PC

PC

Escreverdados

Lerdados 1

Lerdados 2

Readregister 1

Readregister 2

1616

WrWriteiteregisterregister

EscreEscrevvererdadosdados

Lerdados

ALUresult

ALUZeroZero

ALUresult

ALUZeroZero

ID/EX

Endereço

Clock 3

Clock 4

Mux

0

1

Mux

00

11

Mux

00

11

Mux

11

00

Mux

11

00

Mux

00

11

DecodificaçãoDecodificaçãode instrde instruçãoução

sub $11, $2, $3ExExecuçãoecução

lw $10, 20($1)

Registradores

Exten-são desinal

Memória deinstrução

RegistradoresMemória de

dados

Exten-são desinal

EscreEscrevvererdadosdados

Lerdados

Endereço

Memória dedados

FIGURA 6.14.2 Diagramas de pipeline com ciclo único para os ciclos de clock 3 (diagrama superior) e 4(diagrama inferior). No terceiro ciclo de clock do diagrama superior, lw entra no estágio EX. Ao mesmo tempo, subentra em ID. No quarto ciclo de clock (caminho de dados inferior), lw move-se para o estágio MEM, lendo a memória pormeio do endereço encontrado em EX/MEM no início do ciclo de clock 4. Ao mesmo tempo, a ALU subtrai e depois colocaa diferença no EX/MEM ao final do ciclo de clock.

6-14-4 Aprofundando o aprendizado ELSEVIER

4

3232

Inst

rIn

stru

ctio

nuc

tion

IF/ID EX/MEM MEM/WB

Add

Add

Readregister 1

Readregister 2

1616

Writeregister

ID/EX

4

3232

Add AddAddresultresult

Shiftleft 2

Shiftleft 2

Inst

ruct

ion

IF/IDIF/ID EX/MEM MEM/WB

1616

ReadReadregisterregister 11

ReadReadregisterregister 22Writeregister

ALUALUresultresult

ALUZeroZero

ALUALUresultresult

ALUZeroZero

ID/EXID/EX

Clock 5

Clock 6

Mux

00

11

Mux

00

11

Mux

0

1

Mux

11

00

Mux

0

1

Mux

00

11

MemórMemóriaiasub $11, $2, $3

EscrEscrita de vita de voltaoltalw $10, 20($1)

EscrEscrita de vita de voltaoltasub $11, $2, $3

Add AddAddresultresult

PC

PC

Memória deinstrução

Endereço LerLerdados 1dados 1

LerLerdados 2dados 2

Escreverdados

EndereçoEndereço

EscreEscrevvererdadosdados

LerLerdadosdados 11

LerLerdados 2dados 2

Escreverdados

LerLerdadosdados

EndereçoEndereço

Registradores

Exten-são desinal

Memória deinstrução

RegistradoresMemória de

dados

Exten-são desinal

EscreEscrevvererdadosdados

LerLerdadosdados

EndereçoEndereço

Memória dedados

FIGURA 6.14.3 Diagramas de pipeline de ciclo único para os ciclos de clock 5 (diagrama superior)e 6 (diagrama inferior). No ciclo de clock 5, lw completa escrevendo os dados de MEM/WB no registrador 10, esub envia a diferença em EX/MEM para MEM/WB. No próximo ciclo de clock, sub escreve o valor de MEM/WB no regis-trador 11.

Rotulando diagramas de pipeline com controle6.15 [20] <§6.3> Para entender como funciona o controle do pipeline, vamos considerar cinco ins-truções percorrendo o pipeline:

lw $10, 20($1)sub $11, $2, $3and $12, $4, $5or $13, $6, $7add $14, $8, $9

Mostre as instruções no pipeline que precedem o lw como before <1>, before <2>, ..., e as instru-ções após o add como after <1>, after <2>, ... As Figuras de 6.14.5 a 6.14.9 mostram essas instruçõesprosseguindo pelos nove ciclos de clock necessários para concluir a execução, destacando o que estáativo em um estágio e identificando a instrução associada a cada estágio durante um ciclo de clock. Aanálise cuidadosa dessas figuras dará idéia de como funcionam os pipelines. Alguns itens que vocêpode observar:

! Na Figura 6.14.7, você pode ver a seqüência dos números de registrador destino da esquerdapara a direita na parte inferior dos registradores de pipeline. Os números prosseguem para a di-reita durante cada ciclo de clock, com o registrador de pipeline MEM/WB fornecendo o núme-ro do registrador escrito durante o estágio WB.

! Quando um estágio está inativo, os valores das linhas de controle que estão inativas aparecemcomo 0 ou X (para “don’t care”).

! Ao contrário do Capítulo 5, no qual a seqüência de controle exigia hardware especial, a seqüên-cia de controle está embutida na própria estrutura do pipeline. Primeiro, todas as instruções le-vam o mesmo número de ciclos de clock, de modo que não existe controle especial para aduração da instrução. Segundo, toda a informação de controle é computada durante a decodifi-cação da instrução, e depois passada pelos registradores de pipeline.

Usando o mesmo formato da Figura 6.14.5 e começando com o diagrama de pipelining vazio daFigura 6.14.10, desenhe os diagramas de pipeline para a seqüência anterior, por um total de 4 ciclosde clock.

Aprofundando o aprendizado 6-14-5

4

32

Inst

ruct

ion

Add

Readregister 1

Readregister 2

16

Writeregister

ALUresult

ALUZero

Mux

0

1

Mux

0

1

Mux

0

1

Shiftleft 2

Add Addresult

PC

IF/ID EX/MEM MEM/WBID/EX

Clock

Memória deinstrução

Endereço Lerdados 1

Lerdados 2

Escreverdados Registradores

Exten-são desinal

Escreverdados

Lerdados

Endereço

Memória dedados

FIGURA 6.14.4 Um diagrama de pipeline com ciclo único de clock para uso na ilustração da execução dopipeline.

6-14-6 Aprofundando o aprendizado ELSEVIER

InstrInstructiouctio nn[20[20––16]16]

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrALUSr cc

4

InstrInstructiouctio nn[15[15––0]0] ControleControle

ALUALU

Reg

Wr

Reg

Writ

eite

MemReadMemRead

ContrControlol

InstrInstructiouctio nn[15[15––11]11]

EXEX

MM

WBWB

MM

WBWB

WBWB

Inst

rIn

stru

ctio

nuc

tion

IF/ID EX/MEMID/E X

ID:before<1>

EX:before<2>

MEM:before<3>

WB:before<4>

MEM/WB

IF: lw $10, 20($1)

000000

0000

00000000

000000

0000

000000

00

0000

0000

00

0000

11

PC

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDsRegDs tt

ALUSrALUSr cc

4

ALUALUresultresult

ZeroZero

Reg

Wr

Reg

Writ

eite

MM

WBWB

WBWB

Inst

ruct

ion

IF/ID

ID:lw $10, 20($1)

EX:before<1>

MEM:before<2>

WB:before<3>

MEM/WB

IF:sub $11, $2, $3

010010

1111

00010001

000000

0000

000000

00

0000

0000

00

0000

PC

lwContrControlol

X

1

Instructio n[20–16]

Instructio n[15–0]

Instructio n[15–11]

20

$X

$1

10

X

Mem

Wr

Mem

Writ

eite

MemReadMemRead

Mem

Wr

Mem

Writ

eite

Clock 2

Clock 1

Mux

0

1

Mux

00

11

Mux

11

00

Mux

00

11

Mux

0

1

Mux

00

11

Mux

00

11

Mux00

Add

Add

Readregister 1

Readregister 2WrWrititregisterregister

ee

ReadReadregisterregister 11

ReadReadregisterregister 22WrWrititeeregisterregister

ALUALUresultresult

ALUZeroZero

X

10

20

EX/ME MID/E X

ALU

Shiftleft2

Add AddAddresultresult

Shiftleft2

Add AddAddresultresult

WBWB

EXEX

MM

Memória deinstrução

Endereço Lerdados 1

Lerdados 2

EscreEscrevvererdadosdados

Endereço

EscreEscrevvererdadosdados

LerLerdadosdados 11

LerLerdados 2dados 2

EscreEscrevvererdadosdados

LerLerdadosdadosEndereçoEndereço

Registradores

Exten-são desinal

Memória deinstrução

RegistradoresMemória de

dados

Exten-são desinal

EscreEscrevvererdadosdados

LerLerdadosdados

EndereçoEndereço

Memória dedados

ControleControleALUALU

FIGURA 6.14.5 Ciclos de clock 1 e 2. A frase “before <i>” significa a i-ésima instrução antes de lw. A instrução lwno caminho de dados superior está no estágio IF. Ao final do ciclo de clock, a instrução lw está nos registradores de pipelineIF/ID. No segundo ciclo de clock, visto no caminho de dados inferior, o lw passa para o estágio ID, e sub entra no estágioIF. Observe que os valores dos campos de instrução e os registradores de origem selecionados aparecem no estágio ID.Logo, o registrador $1 e a constante 20, os operandos de lw, são escritos no registrador de pipeline ID/EX. O número 10, re-presentando o número do registrador destino de lw, também é colocado em ID/EX. Os bits 15-11 são 0, mas usamos X paramostrar que um campo não desempenha uma função em determinada instrução. O topo do registrador de pipeline ID/EXmostra os valores de controle para lw a serem usados nos estágios restantes. Esses valores de controle podem ser lidos apartir da linha lw da tabela na Figura 6.25.

Aprofundando o aprendizado 6-14-7

Instruction[20–16]

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrALUSr cc

4

Instruction[15–0]

Shiftleft 2R

egW

rR

egW

riteite

MemReadMemRead

ContrControlol

Instruction[15–11]

EXEX

MM

WBWB

MM

WBWB

WBWB

Inst

ruçã

o

IF/ID EX/ME MID/E X

ID:sub $11, $2, $3

EX:lw $10 , . . .

MEM:before<1>

WB:before<2>

MEM/WB

IF:and $12, $4, $5

000000

0000

00000000

010010

1111

000000

11

0000

0000

00

0000

11

PC

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrALUSr cc

4

ZeroZero

Shiftleft 2R

egW

rR

egW

riteite

WBWB

WBWB

Inst

ruçã

o

IF/ID

ID: and $12, $4, $5 EX: sub $11 , . . . MEM: lw $10 , . . . WB: before<1>

MEM/WB

IF: or $13, $6, $7

000000

1010

11001100

000000

1010

101011

00

1111

1100

00

0000

PC

andContrControlol

5

4

Instruction[20–16]

Instruction[15–0]

Instruction[15–11]

X

$5

$4

$3

$2

X

20

10

1210

11

Mem

Wr

Mem

Writ

eite

MemReadMemRead

Mem

Wr

Mem

Writ

eite

Clock 4

Clock 3

Mux

0

1

Mux

0

11

Mux

11

00

Mux

00

1

Mux

0

1

Mux

0

1

Mux

0

1

Mux00

Add

Add

Readregister 1

Readregister 2Writeregister

Readregister 1Readregister 2WrWriteiteregisterregister

Add AddAddresulresultt

ALUresult

ALUZeroZero

Add AddAddresultresult

12

X

X

EX/ME MID/E X

ALUresult

ALU

2

3$2 $1

$3

X

X

11

X

X

11

MM

WBWB

EXEX

MM

ContrControleoleALUALU

Memória deinstrução

Endereço Lerdados 1

Lerdados 2

Escreverdados

Endereço

EscreEscrevvererdadosdados

Lerdados 1

Lerdados 2

EscreEscrevvererdadosdados

LerLerdadosdadosEndereçoEndereço

Registradores

Exten-são desinal

Memória deinstrução

RegistradoresMemória de

dados

Exten-são desinal

EscreEscrevvererdadosdados

Lerdados

Endereço

Memória dedados

ContrControleoleALUALU

FIGURA 6.14.6 Ciclos de clock 3 e 4. No diagrama superior, lw entra no estágio EX no terceiro ciclo de clock, so-mando $1 e 20 para formar o endereço no registrador de pipeline EX/MEM. (A instrução lw é escrita como lw $10,... ao al-cançar EX, pois a identidade dos operandos da instrução não é necessária para EX ou para os estágios subseqüentes. Nessaversão do pipeline, as ações de EX, MEM e WB dependem apenas da instrução e seu registrador destino ou seu endereçode destino.) Ao mesmo tempo, sub entra em ID, lendo os registradores $2 e $3, e a instrução and inicia IF. No quarto ciclode clock (caminho de dados inferior), lw se move para o estágio MEM, lendo a memória por meio do valor em EX/MEMcomo endereço. No mesmo ciclo de clock, a ALU subtrai $3 de $2 e coloca a diferença em EX/MEM, and lê os registrado-res $4 e $5 durante ID, e a instrução or entra em IF. Os dois diagramas mostram os sinais de controle sendo criados no está-gio ID e removidos conforme são utilizados nos estágios de pipe subseqüentes.

6-14-8 Aprofundando o aprendizado ELSEVIER

Instruction[20–16]

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrALUSr cc

4

Instruction[15–0]

Shiftleft2R

egW

rR

egW

riteite

MemReadMemRead

ContrControlol

Instruction[15–11]

EXEX

MM

WBWB

MM

WBWB

WBWB

Inst

ruçã

o

IF/ID

or

EX/MEMID/E X

ID:or $13, $6, $7

EX:and $12 , . . .

MEM:sub $11 , . . .

WB:lw $10, . . .

MEM/WB

IF:add $14, $8, $9

000000

1010

11001100

000000

1010

101011

00

1010

0000

00

1111

1

PC

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrALUSr cc

4

ALUZeroZero

Shiftleft2R

egW

rR

egW

riteite

MM

WBWB

WBWB

Inst

ruçã

o

IF/ID

ID:add $14, $8, $9

EX:or $13 , . . .

MEM:and $12 , . . .

WB:sub $11, . . .

MEM/WB

IF:after<1>

000000

1010

11001100

000000

1010

101011

00

1010

0000

00

1100

PC

addContrControlol

9

11

8

Instruction[20–16]

Instruction[15–0]

Instruction[15–11]

X

$9

$8

$7

$6

X

11 10

1412 11

13

Mem

Wr

Mem

Writ

eite

MemReadMemRead

Mem

Wr

Mem

Writ

eite

Clock 6

Clock 5

Mux

00

11

Mux

0

11

Mux

11

0

Mux

00

1

Mux

0

1

Mux

0

11

Mux

0

1

Mux00

Add

Add

Readregister 1

Readregister 2Writeregister

Readregister 1Readregister 2Writeregister

Add AddAddresulresultt

ALUresult

ALUZeroZero

Add AddAddresultresult

12

X

X

EX/MEMID/E X

resultALU

6

7

10

$6 $4

$5$7

X

X

13

X

X

13 12

WBWB

EXEX

MM

ContrControleoleALUALU

Memória deinstrução

EndereçoEndereço Lerdados 1

Lerdados 2

Escreverdados

Endereço

EscreEscrevvererdadosdados

Lerdados 1

Lerdados 2

Escreverdados

LerLerdadosdados

EndereçoEndereço

Registradores

Exten-são desinal

Memória deinstrução

RegistradoresMemória de

dados

Exten-são desinal

EscreEscrevvererdadosdados

LerLerdadosdados

EndereçoEndereço

Memória dedados

ContrControleoleALUALU

FIGURA 6.14.7 Ciclos de clock 5 e 6. Com add, a instrução final neste exemplo, entrando em IF no caminho superi-or, todas as instruções estão ocupadas. Escrevendo os dados de MEM/WB no registrador 10, lw termina; os dados e o nú-mero do registrador estão em MEM/WB. No mesmo ciclo de clock, sub envia a diferença em EX/MEM para MEM/WB, eo restante das instruções se move para a frente. No ciclo de clock seguinte, sub seleciona o valor em MEM/WB para escre-ver no registrador número 11, novamente encontrado em MEM/WB. As instruções restantes brincam de siga-o-líder: aALU calcula o OR de $6 e $7 para a instrução or no estágio EX, e os registradores $8 e $9 são lidos no estágio ID para a ins-trução add. As instruções após add aparecem como inativas, só para enfatizar o que ocorre para as cinco instruções noexemplo. A frase “after<i>” significa a i-ésima instrução após add.

Aprofundando o aprendizado 6-14-9

InstrInstructionuction[20–16][20–16]

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrcALUSrc

4

InstrInstructionuction[15–0][15–0]

Shiftleft 2R

egW

rR

egW

riteite

MemReadMemRead

ContrControlol

InstrInstructionuction[15–11][15–11]

EXEX

MM

WBWB

MM

WBWB

WBWB

IF/ID EX/MEMID/E X

ID:after<1>

EX:add $14 , . . .

MEM:or $13 , . . .

WB:and $12, . . .

MEM/WB

IF:after<2>

000000

1010

11001100

000000

1010

101011

00

1010

0000

00

1100

0

PC

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrcALUSrc

4

ALUresult

Shiftleft2R

egW

rR

egW

riteite

MM

WBWB

WBWB

IF/ID

ID:after<2>

EX:after<1>

MEM:and $14 , . . .

WB:or $13, . . .

MEM/WB

IF:after<3>

000000

0000

00000000

000000

0000

000000

00

1010

0000

00

1100

PC

ContrControlol

13

InstrInstructionuction[20–16][20–16]

InstrInstructionuction[15–0][15–0]

InstrInstructionuction[15–11][15–11]

14 13

Mem

Wr

Mem

Writ

eite

MemReadMemRead

Mem

Wr

Mem

Writ

eite

Clock 8

Clock 7

Mux

00

11

Mux

00

11

Mux

11

0

Mux

00

11

Mux

00

11

Mux

0

1

Mux

00

11

Mux1

Add

Add

Readregister 1

Readregister 2Writeregister

Readregister 1

Readregister 2Writeregister

Add AddAddresultresult

ALUresult

ALUZeroZero

Add AddAddresultresult

EX/MEMID/E X

ALUZeroZero

12

$8

$9

14

13 12

WBWB

EXEX

MM

Inst

ruçã

oIn

stru

ção

Con-Con-trtroleoleALUALU

Memória deinstrução

Endereço Lerdados 1

Lerdados 2

Escreverdados

EndereçoEndereço

EscreEscrevvererdadosdados

LerLerdadosdados 11

LerLerdados 2dados 2

Escreverdados

LerLerdadosdadosEndereçoEndereço

Registradores

Exten-são desinal

Memória deinstrução

RegistradoresMemória de

dados

Exten-são desinal

EscreEscrevvererdadosdados

LerLerdadosdados

EndereçoEndereço

Memória dedados

ContrControleoleALUALU

FIGURA 6.14.8 Ciclos de clock 7 e 8. No caminho de dados superior, a instrução add expõe o que há por trás, so-mando os valores correspondentes aos registradores $8 e $9 durante o estágio EX. O resultado da instrução or é passado deEX/MEM para MEM/WB no estágio MEM, e o estágio WB escreve o resultado da instrução and em MEM/WB para o re-gistrador $12. Observe que os sinais de controle estão inativos (em 0) no estágio ID, pois nenhuma instrução está sendoexecutada. No ciclo de clock seguinte (desenho inferior), o estágio WB escreve o resultado no registrador $13, completan-do assim o or, e o estágio MEM passa a soma do add em EX/MEM para MEM/WB. As instruções após o add aparecemcomo inativas por questões pedagógicas.

6-14-10 Aprofundando o aprendizado ELSEVIER

WBWB

EXEX

MM

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrALUSrcc

4

ZeroZero

Shiftleft 2R

egW

rR

egW

riteite

MM

WBWB

WBWB

Inst

rIn

stru

ção

ução

IF/ID

ID:after<3>

EX:after<2>

MEM:after<1>

WB:add $14, . . .

MEM/WB

IF:after<4>

000000

0000

00000000

000000

1010

000000

00

1010

0000

00

1100

PC

ContrControlol

14

InstrInstructionuction[20–16][20–16]

InstrInstructionuction[15–0][15–0]

InstrInstructionuction[15–11][15–11]

14

MemReadMemRead

Mem

Wr

Mem

Writ

eite

Clock 9

Mux

00

11

Mux

00

11

Mux

1

0

Mux

00

11

Add

Readregister 1

Readregister 2Writeregister

Add AddAddresultresult

EX/MEMID/EX

ALUALUresultresult

ALU

ContrControleoleALUALU

EndereçoEndereço

EscreEscrevvererdadosdados

LerLerdadosdados 11

LerLerdados 2dados 2

Escreverdados

LerLerdadosdados

EndereçoEndereçoMemória deinstrução

RegistradoresMemória de

dados

Exten-são desinal

FIGURA 6.14.9 Ciclo de clock 9. O estágio WB escreve a soma que se encontra em MEM/WB no registrador $14,completando o add e a seqüência de cinco instruções. As instruções após add aparecem como inativas por questões pe-dagógicas.

Mem

toR

egM

emto

Reg

ALUOpALUOp

BrBranchanch

RegDstRegDst

ALUSrALUSrcc

4ShiftShiftleftleft 22R

egW

rR

egW

riteite

MM

WBWB

WBWB

IF/ID

ID: EX: MEM: WB:

MEM/WB

IF:

000000

0000

00000000

000000

1010

000000

00

0000

0000

00

0000

PC

ContrControlol

InstrInstructionuction[20–16][20–16]

InstrInstructionuction[15–0][15–0]

InstrInstructionuction[15–11][15–11]

MemReadMemRead

Mem

Wr

Mem

Writ

eite

Clock

Mux

00

11

MMuuxx

00

11

MMuuxx

11

00

MMuuxx

00

11

Add

ReadReadregister 1register 1

ReadReadregister 2register 2WrWriteiteregisterregister

AdAddd AddAddresultresult

EX/MEMID/EX

ALUALUresultresult

ALUALUZeroZero

WBWB

EXEX

MM

Inst

rIn

stru

ção

ução

Con-Con-trtroleoleALUALU

Endereço

EscreEscrevvererdadosdados

LerLerdadosdados 11

LerLerdados 2dados 2

EscreEscrevvererdadosdados

LerLerdadosdados

EndereçoEndereçoMemória deinstrução

RegistradoresRegistradoresMemória deMemória de

dadosdados

Exten-são desinal

FIGURA 6.14.10 Um diagrama de pipeline com ciclo único de clock em branco, com controle.

Ilustrando pipelines com forwarding6.16 [20] <§6.4> Podemos usar os diagramas de pipeline de ciclo único de clock para mostrarcomo funciona o forwarding, e também como o controle ativa os caminhos de forwarding. Considerea seqüência de código a seguir, em que as dependências foram destacadas:

sub $2, $1, $3and $4, $2, $5or $4, $4, $2add $9, $4, $2

As Figuras 6.14.11 e 6.14.12 mostram os eventos nos ciclos de clock 3-6 da execução dessas ins-truções. No ciclo de clock 4, a unidade de forwarding vê a escrita da instrução sub do registrador $2no estágio MEM, enquanto a instrução and no estágio EX está lendo o registrador $2. A unidade deforwarding seleciona o registrador de pipeline EX/MEM no lugar do registrador de pipeline ID/EXcomo entrada superior para a ALU, a fim de obter o valor apropriado para o registrador $2. A instru-ção or a seguir lê o registrador $4, que é escrito pela instrução and, e o registrador $2, escrito pela ins-trução sub. Assim, no ciclo de clock 5, a unidade de forwarding seleciona o registrador de pipelineEX/MEM para a entrada superior da ALU e o registrador de pipeline MEM/WB para a entrada infe-rior da ALU. A instrução add a seguir lê o registrador $4, o destino da instrução and, e o registrador$2, que a instrução sub já escreveu. Observe que as duas instruções anteriores escrevem o registrador$4, de modo que a unidade de forwarding precisa selecionar o registrador imediatamente anterior(estágio MEM). No ciclo de clock 6, a unidade de forwarding seleciona assim o registrador de pipeli-ne EX/MEM, contendo o resultado da instrução or, para a entrada superior da ALU, mas usa o valor,que não é de forwarding, do registrador para a entrada inferior da ALU. Usando o diagrama vazio daFigura 6.14.13 e o formato da Figura 6.14.11, desenhe os diagramas de pipeline com ciclo único declock para os ciclos de 3 a 5 durante a execução desta seqüência:

add $1, $1, $3add $4, $2, $1and $5, $4, $1

Ilustrando pipelines com forwarding e stalls6.24 [20] <§6.5> Podemos usar os diagramas de pipeline com ciclo único de clock para mostrarcomo funciona o controle de stalls. As Figuras de 6.14.14 a 6.14.16 mostram o diagrama de cicloúnico para os clocks de 2 a 7 para a seguinte seqüência de código (dependências destacadas).

lw $2, 20($1)and $4, $2,$5or $4, $4,$2add $9, $4,$2

Usando o mesmo formato da Figura 6.14.15, ilustre a execução da seguinte seqüência para os ci-clos de clock de 3 a 6. Use a Figura 6.14.17 para fazer o exercício.

lw $2, 20($1)add $4, $5, $2sub $4, $4, $2

Aprofundando o aprendizado 6-14-11

6-14-12 Aprofundando o aprendizado ELSEVIER

FIGURA 6.14.11 Ciclos de clock 3 e 4 da seqüência de instruções no Exercício 6.16. As linhas mais es-pessas são aquelas ativas em um ciclo de clock, e os números de registradores em itálico e destaque indicam um hazard.A unidade de forwarding é destacada sombreando-a quando estiver realizando forwarding de dados para a ALU. As ins-truções antes de sub aparecem como inativas só para enfatizar o que ocorre com as quatro instruções no exemplo. Os no-mes de operando são usados em EX para o controle do forwarding; assim, eles estão incluídos no rótulo da instruçãopara EX. Os nomes de operando não são necessários em MEM ou WB, de modo que ... é utilizado. Compare isso com asFiguras de 6.14.6 a 6.14.9, mostrando o caminho de dados sem forwarding, onde ID é o último estágio a precisar de in-formações do operando.

Aprofundando o aprendizado 6-14-13

FIGURA 6.14.12 Ciclos de clock 5 e 6 da seqüência de instruções no Exercício 6.16. A unidade de for-warding é destacada quando está realizando forwarding de dados para a ALU. As duas instruções após add aparecem comoinativas só para enfatizar o que ocorre para as quatro instruções no exemplo. As linhas em negrito são aquelas ativas em umciclo de clock, e os números de registrador em itálico e coloridos indicam um hazard.

6-14-14 Aprofundando o aprendizado ELSEVIER

FIGURA 6.14.13 Diagrama de pipeline em branco com caminhos de dados de forwarding.

Aprofundando o aprendizado 6-14-15

FIGURA 6.14.14 Ciclos de clock 2 e 3 da seqüência de instruções no Exercício 6.24 com um load substi-tuindo sub. As linhas em negrito são aquelas ativas em um ciclo de clock, os números de registrador em itálico e em des-taque indicam um hazard, e ... no lugar dos operandos significa que sua identidade é informação não necessária por esse es-tágio. Os valores significativos das linhas de controle, registradores e números de registradores são rotulados nas figuras. Ainstrução and deseja ler o valor criado pela instrução lw no ciclo de clock 3, de modo que a unidade de detecção de hazardfaz um stall nas instruções and e or. Em virtude disto, a unidade de detecção de hazard está destacada.

6-14-16 Aprofundando o aprendizado ELSEVIER

FIGURA 6.14.15 Ciclos de clock 4 e 5 da seqüência de instruções no Exercício 6.24 com um load substi-tuindo sub. A bolha é inserida no pipeline no ciclo de clock 4, e depois a instrução and tem permissão para prosseguir nociclo de clock 5. A unidade de forwarding é destacada no ciclo de clock 5 porque está realizando forwarding de dados de lwpara a ALU. Observe que, no ciclo de clock 4, a unidade de forwarding realiza um forwarding do endereço do lw como sefosse o conteúdo do registrador $2; isso se torna inofensivo pela inserção da bolha. As linhas mais espessas são aquelas ati-vas em um ciclo de clock, e os números de registrador em itálico e destaque indicam um hazard.

Aprofundando o aprendizado 6-14-17

FIGURA 6.14.16 Ciclos de clock 6 e 7 da seqüência de instruções no Exercício 6.24 com um load substi-tuindo sub. Observe que, diferente da Figura 6.14.12, o stall permite que o lw termine, e, por isso, não existe forwardingde MEM/WB no ciclo de clock 6. O registrador $4 para o add no estágio EX ainda depende do resultado de or no EX/MEM,de modo que a unidade de forwarding passa o resultado para a ALU. As linhas em negrito mostram as linhas de entrada daALU ativas em um ciclo de clock, e os números de registrador em itálico indicam um hazard. As instruções após o add apa-recem como inativas por questões pedagógicas.

Exercícios diversos6.5 [5] <§6.1> Como poderíamos modificar o código a seguir para utilizar um delay slot?

Loop: lw $2, 100($3)addi $3, $3, 4beq $3, $4, Loop

6.10 [5] <§6.2> Para cada registrador de pipeline na Figura 6.22, rotule cada parte do registrador depipeline com o nome do valor carregado no registrador. Determine a extensão de cada campo embits. Por exemplo, o registrador de pipeline IF/ID contém dois campos, um deles sendo um campo deinstrução que possui 32 bits de largura.

6.11 [15] <§§3.6, 6.2> Usando a Figura 3.13 como base, descubra uma estrutura de caminho de da-dos em pipeline razoável para a adição de ponto flutuante, e integre os registradores de ponto flutu-ante e a memória de dados à sua figura para produzir uma figura semelhante à Figura 6.11, excetoque seu diagrama também deve conter um pipeline alternativo para instruções de adição de pontoflutuante. Não se preocupe muito com os atrasos associados a cada uma das funções na Figura 3.13.Você deverá simplesmente assumir que a soma dos atrasos é muito grande e, por isso, exige que vocêuse 2 ou 3 ciclos para realizar a adição de ponto flutuante. A adição deverá ser mantida em pipeline,de modo que uma nova instrução de adição de ponto flutuante possa ser iniciada a cada ciclo, supon-do que não haja dependências (você pode ignorar as dependências para esse problema).

6.20 [20] <§§6.4, 6.5> Considere uma seqüência de instruções utilizada para uma cópia da memó-ria para a memória:

lw $2, 100($5)sw $2, 200($6)

A Seção de “Detalhamento” da página 310 do texto discute essa situação e indica que o hardwarede forwarding adicional pode melhorar seu desempenho. Mostre os acréscimos necessários ao cami-nho de dados da Figura 6.33 para permitir que um código como esse seja executado sem stalls. Inclua

6-14-18 Aprofundando o aprendizado ELSEVIER

FIGURA 6.14.17 Diagrama de pipeline em branco com hardware de stall.

equações de forwarding (como aquelas que aparecem nas páginas 306-310) para todos os sinais decontrole para quaisquer multiplexadores novos ou modificados no seu caminho de dados. Finalmen-te, reescreva a fórmula de stall da página 311 de modo que essa seqüência de código não gere stall.

6.25 [20] <§6.5> A unidade de forwarding poderia ser movida para o estágio de ID e as decisões deforwarding poderiam ser feitas mais cedo. Os resultados dessas decisões precisariam ser passadosadiante com a instrução e utilizados no estágio EX quando o forwarding real ocorresse. Essa modifi-cação agilizaria o estágio EX e poderia permitir uma possível melhoria no tempo do ciclo. Realize amodificação. Ofereça um caminho de dados revisado e uma descrição das mudanças necessárias.Como o registrador ID/EX mudou? Ofereça novas equações de forwarding para substituir as queaparecem nas páginas 306-310.

6.26 [15] <§§6.2–6.5> Nos exercícios do Capítulo 5, exploramos as implicações de ter instruçõesload e store sem deslocamento. Como essa modificação no conjunto de instruções afetaria uma im-plementação em pipeline? Descreva as mudanças no caminho de dados e o impacto sobre o desem-penho. Não se esqueça de incluir uma discussão sobre forwarding na sua resposta.

6.27 [10] <§§6.2–6.5> A ISA 80x86 possui instruções aritméticas que podem acessar a memóriadiretamente. Escreva um ou dois parágrafos explicando por que seria difícil incluir essa instrução nopipeline MIPS descrito neste capítulo. (Dica: você pode ter de incluir um ou mais estágios adicionaisno pipeline.)

6.28 [30] <§6.5, Apêndice C> Usando o Apêndice C e a resposta do Exercício 6.23, projete o hard-ware para implementar a unidade de forwarding. (Dica: para decidir se os números de registrador sãoiguais, tente usar uma porta OR exclusiva. Veja a Seção de “Detalhamento” na página B-36 doApêndice B.)

6.31 [10] <§6.6> Uma extensão do conjunto de instruções MIPS possui duas novas instruções,chamadas movn (move if not zero) e movz (move if zero). Por exemplo, a instrução movn $8, $11,$4 copia o conteúdo do registrador 11 para o registrador 8, desde que o valor no registrador 4 não sejazero (caso contrário, ela não faz nada). A instrução movz é semelhante, mas a cópia ocorre somentese o valor do registrador for zero. Mostre como usar as novas instruções para colocar o que for maior,o valor do registrador 8 ou o valor do registrador 9, no registrador 10. Se os valores forem iguais, co-pie qualquer um para o registrador 10. Você pode usar o registrador 1 como um registrador extra parauso temporário. Não use quaisquer desvios condicionais.

6.32 [10] <§6.6> A solução para o Exercício 6.31 deverá envolver a execução de menos instruçõesdo que seriam necessárias usando desvios condicionais. No entanto, às vezes, a reescrita do códigopara usar movn e movz em vez de desvios condicionais não reduz o número de instruções executa-das. Apesar disso, mesmo que o uso de movn e movz não reduza o número de instruções executadas,isso ainda pode tornar o programa mais rápido se estiver sendo executado em um caminho de dadosem pipeline. Explique por quê.

Aprofundando o aprendizado 6-14-19