AOCO

-

Upload

nadiascarvalho -

Category

Documents

-

view

169 -

download

66

description

Transcript of AOCO

Arquitetura e Organização de Computadores

Exercícios

António José Araújo

João Canas Ferreira

Raul Moreira Vidal

Mestrado Integrado em Engenharia Informática e Computação

Setembro de 2015

Conteúdo

1 Aritmética binária 11.1 Exercícios resolvidos . . . . . . . 11.2 Exercícios propostos . . . . . . . 7

2 Vírgula flutuante 102.1 Exercícios resolvidos . . . . . . . 102.2 Exercícios propostos . . . . . . . 16

3 Circuitos combinatórios 183.1 Exercícios resolvidos . . . . . . . 183.2 Exercícios propostos . . . . . . . 26

4 Circuitos sequenciais 324.1 Exercícios resolvidos . . . . . . . 324.2 Exercícios propostos . . . . . . . 39

5 Desempenho 445.1 Exercícios resolvidos . . . . . . . 445.2 Exercícios propostos . . . . . . . 49

6 Linguagem assembly 536.1 Sumário das instruções MIPS-32 53

6.2 Exercícios resolvidos . . . . . . . 546.3 Exercícios propostos . . . . . . . 63

7 Organização do processador MIPS 677.1 Exercícios resolvidos . . . . . . . 677.2 Exercícios propostos . . . . . . . 72

8 Memória Cache 758.1 Exercícios resolvidos . . . . . . . 758.2 Exercícios propostos . . . . . . . 77

9 Soluções dos exercícios propostos 819.1 Aritmética binária . . . . . . . . 819.2 Vírgula flutuante . . . . . . . . . 839.3 Circuitos combinatórios . . . . . 849.4 Circuitos sequenciais . . . . . . . 899.5 Desempenho . . . . . . . . . . . . 919.6 Linguagem assembly . . . . . . . 939.7 Organização do processador MIPS 979.8 Memória Cache . . . . . . . . . . 98

Esta coletânea reúne exercícios resolvidos e propostos sobre a matéria lecionada em 2014/15 naunidade curricular de Arquitetura e Organização de Computadores do 1o ano do Mestrado Inte-grado em Engenharia Informática e Computação da Faculdade de Engenharia da Universidadedo Porto.

1 Aritmética binária

1.1 Exercícios resolvidos

Exercício 1Realizar as conversões de base indicadas.

7210 =?2 =?16a) 25910 =?2 =?16b) 11102 =?10 =?16c)

100000,112 =?10 =?16d) 1BEEF16 =?2e)

a) A conversão de decimal para qualquer base de representação pode ser feita por divisõessucessivas pela base pretendida ou realizando a decomposição do número em potências dessabase. Optando por este segundo processo, resulta

7210 = 64 + 8 = 26 + 23 = 1× 26 + 0× 25 + 0× 24 + 1× 23 + 0× 22 + 0× 21 + 0× 20

= 10010002

Relativamente à conversão para hexadecimal, a forma mais simples de a realizar consiste emconsiderar a representação binária e formar grupos de 4 bits, da direita para a esquerda, edepois fazer a correspondência entre cada um desses grupos e o respetivo símbolo hexadeci-mal.

100 1000 = 48H4 8

Nota: O índice ’H’, tal como ’16’, indica uma representação em hexadecimal.

b)25910 = 256 + 2 + 1 = 28 + 21 + 20 = 1000000112

1000000112 = 1 0000 0011 = 103H1 0 3

c)11102 = 23 + 22 + 21 = 1410

1110 = EH

E

Arquitetura e Organização de Computadores Pág. 1 de 100

Aritmética binária — Exercícios resolvidos

d)100000,112 = 25 + 2−1 + 2−2 = 32,7510

Como se trata de um número fracionário, na conversão de binário para hexadecimal, osgrupos de 4 bits formam-se a partir da vírgula.

100000,112 = 10 0000, 1100 = 20,CH

2 0 C

e)1BEEFH = 1 B E E F = 110111110111011112

0001 1011 1110 1110 1111

Exercício 2Efetue as seguintes operações aritméticas binárias, considerando os operandos representa-dos como números sem sinal, isto é, números positivos.

101110 + 100101a) 1110010− 1101101b)

1001011× 11001c) 1101000÷ 100d)

As regras de cálculo são idênticas às regras usadas em base 10.

a)101110

+1001011010011

b)01 0

11�1�00�10−1101101

101

c)1001011× 110011001011

1001011+100101111101010011

d) Nesta divisão ocorre uma situação particular: o divisor é uma potência de 2 (1002 = 22 = 4).Nestas circunstâncias, o quociente pode ser obtido deslocando os bits do dividendo n posiçõespara a direita, o que corresponde a subtrair n ao expoente de cada potência de base 2 dadecomposição do dividendo. Neste exercício n = 2, pelo que, 1101000÷ 100 = 110102.

Arquitetura e Organização de Computadores Pág. 2 de 100

Aritmética binária — Exercícios resolvidos

Exercício 3Represente os seguintes números decimais em sinal e grandeza e em complemento para 2com 6 bits.

+12a) −12b) −1c) +32d)

a) 12 = 8 + 4 = 11002

• Sinal e grandeza: sendo o número positivo, o bit de sinal é 0; a grandeza, escrita em 5bits, é 01100. Assim, 12 = 0011002.

• Complemento para 2: a representação de um número positivo em complemento para2 é a mesma do número sem sinal (binário puro), respeitando porém a largura derepresentação. Portanto, 12 = 0011002.

b) A grandeza de −12 é 12 = 11002.

• Sinal e grandeza: sendo o número negativo, o bit de sinal é 1; a grandeza é codificadacom 5 bits, 01100. Assim, −12 = 1011002.

• Complemento para 2:A representação de um número negativo em complemento para 2 pode ser obtida apartir da representação binária do simétrico do número. Para tal, copiam-se todos osbits da direita para a esquerda até encontrar o primeiro 1, que ainda é copiado, e apartir daí complementam-se os restantes bits. Embora existam outros processos, este éum processo expedito.Assim, partindo de 12 = 0011002 obtém-se −12 = 1101002.

c) • Sinal e grandeza: −1 = 1000012.

• Complemento para 2: tendo em consideração o que foi descrito na alínea anterior,1 = 0000012, pelo que −1 = 1111112.

d) O número em causa é 32 = 25 = 1000002.

• Sinal e grandeza: a grandeza de 32 não se consegue codificar com apenas 5 bits, peloque o valor 32 não é representável no formato pretendido.

• Complemento para 2: o valor 32 também não é representável com 6 bits; é um númeropositivo e no entanto 1000002 representa um número negativo (MSB=1).

Com 6 bits, o maior número representável é 26−1 − 1 = 31.

Arquitetura e Organização de Computadores Pág. 3 de 100

Aritmética binária — Exercícios resolvidos

Exercício 4Considere a representação binária dos valores C116 e A716 com 8 bits.

a) Indique o valor decimal correspondente, admitindo que são interpretadas como núme-ros:

positivos;i) em sinal e grandeza;ii)

em complemento para dois.iii)

b) Indique a gama de valores representáveis considerando a forma complemento para 2.

c) Admitindo que a referida representação se encontra em complemento para dois, efetuea sua adição em binário e comente o resultado.

a) C116 = 110000012 e A716 = 101001112

i)110000012 = 27 + 26 + 20 = 128 + 64 + 1 = 193

101001112 = 27 + 25 + 22 + 21 + 20 = 128 + 32 + 4 + 2 + 1 = 167

ii)1 1000001 = −65− 26 + 20

1 0100111 = −39− 25 + 7

iii) Os valores são ambos negativos.

110000012compl. 2−→ 001111112 = 63

Este é o valor simétrico do número a identificar. Logo, 110000012 interpretado emcomplemento para 2, resulta no decimal −63.

101001112compl. 2−→ 010110012 = 89

Da mesma forma, 101001112 interpretado em complemento para 2, resulta no decimal−89.

b) Com 8 bits conseguem escrever-se 28 = 256 números. Considerando que metade são númerosnegativos e a outra metade corresponde a números positivos, incluindo o 0, resulta o seguinteintervalo de representação: [−128;+127]. Ao contrário do que sucede em sinal e grandeza, o0 só tem uma representação.

De forma mais genérica, em complemento para 2, a gama de representação correspondentea n bits é:

[−2n−1; +2n−1 − 1]

Arquitetura e Organização de Computadores Pág. 4 de 100

Aritmética binária — Exercícios resolvidos

c) A soma faz como para números sem sinal, ignorando o transporte a partir do bit maissignificativo.

11000001+10100111

�101101000

O resultado encontrado (011010002) está incorreto, porque a adição de dois números negati-vos não pode resultar num número positivo. Ocorre portanto, overflow.Pode confirmar-se esta conclusão em decimal: (−63) + (−89) < −128, isto é, a soma não érepresentável com 8 bits.

Exercício 5Admitindo que A = 110012 e B = 111012 se encontram representados em complementopara 2 com 5 bits, calcule A+B e indique, justificando, se ocorre overflow.

Efetuando os cálculos:11001

+11101

�110110

Como se trata de uma adição em complemento para 2, o carry que ocorreu ao somar os bitsmais significativos deve ignorar-se. A ocorrência deste carry não deve ser interpretada comoocorrência de overflow. Logo, A+B = 10110.

O resultado encontrado é válido no formato especificado, pois não ocorre overflow, porque daadição de dois números negativosresultou um número negativo.

Exercício 6Considere dois números binários com 6 bits, M = 1011002 e N = 1100102. M estárepresentado em sinal e grandeza e N está representado em complemento para 2.

a) Escreva M em formato hexadecimal e N em formato decimal.

b) Indique, justificando, qual dos números tem maior grandeza.

c) Mostre que em complemento para 2 a operação M +N não produz overflow.

a) A conversão para hexadecimal é direta:

M = 10 1100 = 2CH

2 C

Como N está em complemento para 2 e é negativo, −N = 001110 = 14, pelo que N = −14.

b) Como M está definido em sinal e grandeza e são usados 6 bits, a grandeza é dada pelos 5bits menos significativos.

|M | = 01100 (= 1210)

Quanto a N , conclui-se da alínea anterior que

|N | = −N = 01110 (= 1410)

Conclusão: N é o número que possui maior grandeza.

Arquitetura e Organização de Computadores Pág. 5 de 100

Aritmética binária — Exercícios resolvidos

c) O número M está definido em sinal e grandeza e é negativo, pelo que deve ser representadoem complemento para 2 antes de ser operado.

−M = 001100compl. 2−→ M = 110100

N já se encontra em complemento para 2, pelo que se pode então calcular M +N :

110100+110010

�1100110

Não há overflow, pois os operandos são negativos e o resultado encontrado também é negativo.

Exercício 7Os valores X = 101111002 e Y = 101001102 estão representados com 8 bits. Determineo menor número de bits necessário para representar corretamente X + Y , supondo que osoperandos estão representados em:

sinal e grandeza;a) complemento para 2.b)

a) Representação em sinal e grandeza:

X = 1 0111100 e Y = 1 0100110

S G S G

Para calcular X + Y é necessário somar as grandezas de X e Y , operação esta realizada em7 bits.

0111100+01001101100010

A grandeza resultante é representável em 7 bits. Como tal, e tendo em consideração o bit desinal, o menor número de bits necessário para a representação de X +Y em sinal e grandezaé 8.

b) Representação em complemento para 2:

X+Y: 10111100+10100110

�101100010

Estão a somar-se dois números com o mesmo sinal (negativos), mas o resultado alcançadocom 8 bits apresenta sinal diferente (positivo). Quer isto dizer que ocorre overflow ao rea-lizar a operação com 8 bits. Portanto, para que X + Y seja corretamente representado emcomplemento para 2, o número mínimo de bits a considerar deverá ser 9.

Arquitetura e Organização de Computadores Pág. 6 de 100

Aritmética binária — Exercícios propostos

Exercício 8Considere a representação em complemento para 2 dos valores X e Y indicada:

X = 1100102 e Y = 1010112

a) Determine o valor decimal de X e Y .

b) Calcule X − Y e X + Y . Comente os resultados.

a) X e Y são negativos, pelo que podem obter-se os números simétricos calculando o comple-mento para 2:

−X = 0011102 = 23 + 22 + 21 = 14

−Y = 0101012 = 24 + 22 + 20 = 21

Logo, X = −14 e Y = −21.

b) A diferença pode ser calculada pela adição do simétrico:

X − Y = X + (−Y ) : 110010+010101

�1000111

Não ocorre overflow, porque os operandos têm sinais opostos. O resultado é por isso correto.

X + Y : 110010+101011

�1011101

Ocorre overflow, porque os operandos têm o mesmo sinal e o resultado tem sinal oposto. Poreste motivo, o resultado é errado, pois não é representável com os 6 bits considerados.

1.2 Exercícios propostos

Exercício 9Em cada alínea, considere o número dado e represente-o nos sistemas de numeração indicados.

25610 =?2 =?16a) 204710 =?2 =?16b) 24,2510 =?2 =?16c)

4,210 =?2 =?16d) 100002 =?10 =?16e) 100,0012 =?10 =?16f)

1E16 =?2 =?10g) ABCD16 =?10 =?2h) AB,C16 =?10 =?2i)

111010 =?16j)

Arquitetura e Organização de Computadores Pág. 7 de 100

Aritmética binária — Exercícios propostos

Exercício 10Efetue as seguintes operações aritméticas binárias, considerando os operandos representadoscomo números sem sinal, isto é, números positivos.

110101 + 11001a) 101,01 + 100,111b) 101110− 100101c)

1000010− 101101d) 11011101− 1100011e) 11011101− 11000,11f)

1011× 100g)

Exercício 11Considere os números decimais +3, +2 e −3. Nas alíneas seguintes admita a representação emsinal e grandeza com 4 bits.

a) Escreva os números em binário.

b) Calcule 3 + 2 e 2 + (−3).

c) Calcule 3 + 14 e comente o resultado.

Exercício 12Enumere os valores decimais que se podem representar com 4 bits usando as representações emsinal e grandeza e em complemento para 2. Em ambos os casos, indique a gama de representaçãona forma de um intervalo, relacionando os valores extremos (maior positivo e menor negativo)com o número de bits.

Exercício 13Recorrendo a 8 bits, represente em sinal e grandeza e em complemento para 2, os seguintesnúmeros decimais:

18a) 49b) −49c)

−3d) −100e) 115f)

−127g) −128h)

Exercício 14Considere os números M = 3316 e N = 3310 representados por 8 bits.

a) Calcule M +N em binário, supondo que M e N são números sem sinal.

b) Admitindo que os valores estão representados em complemento para 2, diga se ocorre overflowao calcular N −M .

Exercício 15Admitindo que P e Q representam dois números binários em complemento para dois, com 8 bits,efetue a sua adição binária e interprete o resultado.

P = DEH e Q = A3Ha) P = 8CH e Q = D3Hb) P = 8CH e Q = 74Hc)

Arquitetura e Organização de Computadores Pág. 8 de 100

Aritmética binária — Exercícios propostos

Exercício 16Considere os seguintes números binários: X = 11100011 e Y = 01001000.

a) Indique o valor decimal de X e Y , para os casos de representação sem sinal e representaçãoem complemento para 2.

b) Calcule X + Y para ambas as representações de 8 bits e comente os resultados obtidos.

Exercício 17Considere os números P = 11110102 e Q = 01000102 com 7 bits.

a) Escreva P em hexadecimal e Q em decimal.

b) Calcule P +Q e comente o resultado considerando que P e Q representam números:

sem sinal;i) em complemento para 2.ii)

Exercício 18Considere os números M = 4AH e N = A4H representados em complemento para 2 com 8 bits.

a) Escreva M em binário.

b) Determine o valor decimal de N .

c) Calcule M −N e N −M , justificando se ocorre overflow.

Exercício 19Considere os números S = 110010002 e T = 000100012 representados em complemento para 2com 8 bits.

a) Determine o valor decimal de S e T .

b) Represente S e T em sinal e grandeza.

c) Calcule S + T em sinal e grandeza e comente o resultado encontrado.

Exercício 20Considere os números de 8 bits expressos, nas bases indicadas, por: X2 = 10111100, Y10 = 73 eZ16 = 9E.

a) Escreva Y em hexadecimal e Z em binário.

b) Calcule X + Z, considerando que os operandos X e Z estão em complemento para 2, ejustifique se ocorre overflow.

c) Calcule o maior número N , em complemento para 2 com 8 bits, que adicionado a X conduza uma soma negativa.

Arquitetura e Organização de Computadores Pág. 9 de 100

2 Vírgula flutuante

2.1 Exercícios resolvidos

Exercício 1A representação dos números reais X e Y no formato de precisão simples da norma IEEE754 é a seguinte:

X: C3800000H Y : 001111111000000000000000000000002

a) Calcule o expoente real do número codificado em X.

b) Determine o sinal de X + Y .

c) Justifique a afirmação: Sendo X um número qualquer, X × Y = X.

a)X = C3800000H = 1 10000111 000000000000000000000002

EX = 135

O expoente real de X é:Ereal

X = 135− 127 = 8

b) Como EY = 127, EX > EY . Então |X| > |Y | e portanto,

SX+Y = SX = 1

ou seja, X + Y é um número negativo.

c) Como EY = 127, ErealY = 0.

Porque os 23 bits da mantissa de Y são nulos, MY = 1,0.

Então, conclui-se que Y = 1 e por isso, para qualquer X, tem-se X × Y = X.

Exercício 2Considere Y = 25,2510 e o número real X cuja representação em formato IEEE 754(precisão simples) é BF40000016.

a) Mostre a representação de Y no formato IEEE 754 (em binário).

b) Calcule X × Y , indicando claramente todos os passos efetuados.

Arquitetura e Organização de Computadores Pág. 10 de 100

Vírgula flutuante — Exercícios resolvidos

a) Pretende-se mostrar Y em binário no contexto da representação em vírgula flutuante comprecisão simples (32 bits).

Y = 25,2510 = 24 + 23 + 20 + 2−2 = 11001,012 = 1,1001012 × 24

• SY = 0

• EY = ErealY + 127 = 4 + 127 = 131 = 100000112

• MY = 1,1001012

Resulta então:Y = 010000011100101 00 · · · 0︸ ︷︷ ︸

17 0’s

b)X = BF40000016 = 1 01111110 100 · · · 02

SX EX fX

Então:

• SX×Y = 1

• EX×Y = EX + EY − 127 = (131 + 126)− 127 = 130 = 100000102

• MX×Y : (em binário)

1,1001010 · · · 0×1,1000000 · · · 00 0000000 · · · 0· · ·

11001010 · · · 011001010 · · · 0

10,01011110 · · · 0

A necessidade de normalizar a mantissa resultante leva ao incremento do expoente calculado:

MX×Y = 10,01011110 · · · 02 = 1,001011112 × 21

Assim, EX×Y = 13110 = 100000112, pelo que

X × Y = 11000001100101111 00 · · · 0︸ ︷︷ ︸15 0’s

Exercício 3Considere o número cuja representação em hexadecimal é C1200000H. Indique o valordecimal correspondente, se assumir que o número está representado:

a) como inteiro sem sinal;

b) em complemento para 2;

c) em vírgula flutuante com precisão simples.

Arquitetura e Organização de Computadores Pág. 11 de 100

Vírgula flutuante — Exercícios resolvidos

a) A representação binária do número é:

C1200000H = 1100 0001 0010 0000 0000 0000 0000 00002

Interpretando este número como um inteiro sem sinal, o valor decimal correspondente édeterminado com base na posição que cada bit ocupa. Assim:

110000010010000000000000000000002 = 231 + 230 + 224 + 221

= 221 × (210 + 29 + 23 + 20)= 2× 210 × 210 × (1024 + 512 + 9)= 2097152× 1545= 324009984010

Nota: É admissível apresentar a solução na forma de uma soma de potências de 2.

b) C1200000H = 1100 0001 0010 0000 0000 0000 0000 00002

Interpretando este número dado em complemento para 2 e atendendo a que é um númeronegativo (MSB=1), o decimal correspondente pode ser determinado depois de obter o si-métrico correspondente. Este pode ser obtido por aplicação da regra prática que consisteem copiar todos os bits da direita para a esquerda até ser encontrado o primeiro 1 e depoiscomplementar os restantes. Assim:

110000010010000000000000000000002↓ ↓−01111101110000000000000000000002

= 229 + 228 + 227 + 226 + 225 + 223 + 222 + 221

= 105486745610

Portanto, C1200000H representa -105486745610 em complemento para 2.

c) Assumindo o formato de vírgula flutuante, a interpretação do padrão de bits é:022233031

1 10000010 01000000000000000000000

↓ ↓ ↓S = − E = 130 M = 1,01

Como o expoente está representado em excesso 127, o expoente real é 3. Então, o númerodecimal correspondente será:

−1,012 × 23 = −10102 = −1010

Arquitetura e Organização de Computadores Pág. 12 de 100

Vírgula flutuante — Exercícios resolvidos

Exercício 4Sejam X e Y dois números reais, representados em vírgula flutuante com o formato deprecisão simples da norma IEEE 754 da seguinte forma:

X: 110000110000001100000000000000002Y : 110000110111110000000000000000002

a) Mostre que X é um número inteiro.

b) Calcule o número Z que verifica a condição X + Z = 0.

c) Mostre que o expoente real de X + Y é 8.

a)X = 1 10000110 000001100000000000000002

− EX = 134 MX = 1,0000011

O expoente real de X é:Ereal

X = 134− 127 = 7

Logo,X10 = −1,00000112 × 27 = −100000112 = −13110

b)X+ Z = 0 ⇔ Z = −X

Em termos de representação em vírgula flutuante

SZ = −SX

EZ = EX

MZ = MX

Logo,Z = 0100001100000011 00 · · · 02︸ ︷︷ ︸

16 0’s

c)Ereal

X+Y = ErealY ≡ Ereal

X = 7

Contudo, ao somar as mantissas, o resultado pode não estar normalizado:

MX : 1,0000011MY : +1,1111100

MX+Y 10,1111111 = 1,011111112 × 21

Logo, o expoente indicado inicialmente tem de ser incrementado, resultando

ErealX+Y = 8

Arquitetura e Organização de Computadores Pág. 13 de 100

Vírgula flutuante — Exercícios resolvidos

Exercício 5Os números reais X, Y e Z estão representados no formato de precisão simples da normaIEEE 754.

a) Sendo X representado por 234567654328, indique o seu sinal.

b) Complete, com os bits em falta, os campos da seguinte igualdade:

Y = + ×23 = 001010 ... 0

1 bit 8 bits 23 bits

c) Qual é o número Z tal que o valor de Y ×Z é representado por 110000011001010 · · · 02?

a)X = 234567654328 = 1︸︷︷︸

↓

00111001︸ ︷︷ ︸EX

01110111110101100011010︸ ︷︷ ︸fX

−

X é negativo.

Note-se que a conversão de cada dígito octal origina 3 bits e por essa razão X2 devia possuir33 bits. Porém, a representação de X2 em vírgula flutuante é constituída por 32 bits, que noseu conjunto correspondem a X8, pois o dígito mais significativo (2) pode escrever-se como0102 ou 102.

b)Y > 0 ⇒ SY = 0Ereal

Y = 3 ⇒ EY = ErealY + 127 = 130 = 100000102

fY = 0,00101 ⇒ MY = 1,001012

Daqui resulta

Y = +1,001012 × 23 = 0 10000010 001010...0

1 bit 8 bits 23 bits

c)SY×Z = − ⇒ SZ = −SY = −EY×Z = EY + EZ − 127⇔ 131 = 130 + EZ − 127⇔ EZ = 128MY×Z ≡MY ⇒ MZ = 1,0

Logo,Z = 1 10000000 00...0

SZ EZ fZ

Arquitetura e Organização de Computadores Pág. 14 de 100

Vírgula flutuante — Exercícios resolvidos

Exercício 6Nesta questão, todos os números reais estão representados em vírgula flutuante (formatode precisão simples da norma IEEE 754).

a) Determine o número X cuja representação é dada por010000100001110100000000000000002.

b) Considerando um segundo número Y em que os 23 bits da sua mantissa são nulos,calcule:

i) a mantissa de X × Y ;

ii) o expoente de Y , sabendo que o expoente resultante de X ×Y , representado nosseus 8 bits, é 100000002.

a)X = 0 10000100 00111010000000000000000

+ EX = 132 MX = 1,0011101

O expoente real de X é:Ereal

X = 132− 127 = 5

Logo,X10 = +1,00111012 × 25 = 100111,012 = 39,2510

b) i) Como os 23 bits da parte representável (parte fracionária) da mantissa são nulos,conclui-se que MY = 1,fY = 1,0. Assim,

MX×Y = MX ×MY = MX = 1,00111012

ii) O expoente do produto de dois números em vírgula flutuante é dado pela soma dosexpoentes dos operandos menos o excesso 127. O expoente assim calculado nem sempreconstitui o expoente definitivo do resultado, pois se o produto das mantissas não resultarnormalizado então o expoente deve ser ajustado de acordo com a normalização. Porém,neste exercício não acontece tal situação porque é dito que MY = 1,0.Assim,

EX×Y = EX + EY − 127

128 = 132 + EY − 127

EY = 123 (ErealY = −4)

Arquitetura e Organização de Computadores Pág. 15 de 100

Vírgula flutuante — Exercícios propostos

2.2 Exercícios propostos

Exercício 7Considere que 110000011011000000000000000000002 é a representação de um número em vírgulaflutuante segundo a norma IEEE 754. Determine:

a mantissa do número;a) o expoente do número;b)

o valor decimal representado.c)

Exercício 8Represente em vírgula flutuante, no formato de precisão simples (32 bits) da norma IEEE 754,os seguintes números:

31,25a) −0,625b) 0c) 1026,5d)

Exercício 9Considere os números decimais A = 33 e B = −2,875.

a) Represente A e B em vírgula flutuante, no formato de 32 bits definido na norma IEEE 754.

b) Efetue as operações seguintes em vírgula flutuante no formato de 32 bits:

A+Bi) B −Aii) 3×Biii)

c) Represente o resultado das operações anteriores em decimal e verifique se corresponde aovalor esperado.

Exercício 10Dois números V1 e V2 estão representados em vírgula flutuante no formato de 32 bits. Os seusvalores, expressos em hexadecimal, são:

V1: 421D0000H V2: C0000000HCalcule:

−V2a) V1 + V2b) V2 − V1c) V1 × V2d)

Exercício 11Seja um número real X, cuja representação em vírgula flutuante (norma IEEE 754, com 32 bits)é 3F400000H. Considere também Y = 11,62510.

a) Apresente em binário a representação de Y no mesmo formato.

b) Calcule X + Y em vírgula flutuante, indicando claramente todos os passos efetuados.

Arquitetura e Organização de Computadores Pág. 16 de 100

Vírgula flutuante — Exercícios propostos

Exercício 12Considere a representação em vírgula flutuante, norma IEEE 754, com 32 bits. Sendo A umnúmero real, cuja representação nesse formato é 40400000H, e sendo B = −10,2510:

a) apresente a representação binária de B no mesmo formato.

b) calcule A−B em vírgula flutuante, indicando claramente todos os passos efetuados. No final,converta o resultado para decimal.

Exercício 13Considere que S e T representam dois números em vírgula flutuante no formato de precisãosimples definido pela norma IEEE 754:

S:110000010100000000000000000000002 T : 110000011011000000000000000000002

a) Indique a representação de S em hexadecimal.

b) Mostre como se realiza a adição de S e T , indicando claramente todos os passos efetuados.

Exercício 14No formato de precisão simples da norma IEEE 754, os números X e Y são representados por

X: C3800000H e Y : 001111111000000000000000000000002.Das afirmações seguintes indique a correta, fundamentando a sua escolha.

A. O expoente real de X é 8.B. X − Y é um número positivo.C. O expoente real de X é 8 e Y é um número negativo.D. X > Y .

Arquitetura e Organização de Computadores Pág. 17 de 100

3 Circuitos combinatórios

3.1 Exercícios resolvidos

Exercício 1Simplifique algebricamente as seguintes funções booleanas usando teoremas da álgebra deBoole.

a) F (A,B,C) = A·B +A+B +A·C.

b) F (A,B,C) = (A+B + C)·(A+B + C)·(A+B + C)·(A+B + C).

c) F (X,Y, Z) = X +X ·Z +X ·Y .

d) G(X,Y, Z) = X ·Y ·Z +X ·Y ·Z +X ·Y ·Z.

e) F (A,B,C) = A·(B + C) +B ·C.

a) F (A,B,C) = A·B +A+B +A·C= A·B +A·B +A·C= A·(B +B) +A·C= A+A·C= A·(1 + C)= A

b) F (A,B,C) = (A+B + C)·(A+B + C)·(A+B + C)·(A+B + C)

=((A+B) + (C ·C)

)·((A+B) + (C ·C)

)= (A+B)·(A+B)

= (A+A)·B= B

c) F (X,Y, Z) = X +X ·Z +X ·Y= X ·(1 + Y ) +X ·Z= X +X ·Z= X + Z

d) G(X,Y, Z) = X ·Y ·Z +X ·Y ·Z +X ·Y ·Z= X ·Y (Z + Z) +X ·Y ·Z= Y ·(X +X ·Z)

= Y ·(X + Z)

= X ·Y + Y ·Z

Arquitetura e Organização de Computadores Pág. 18 de 100

Circuitos combinatórios — Exercícios resolvidos

e) F (A,B,C) = A·(B + C) +B ·C= A·(B + C) +B ·C= A·(B ·C) +B ·C ·(A+A)

= A·B ·C +A·B ·C +B ·C ·A+A·B ·C= A·(B ·C +B ·C) +B ·C ·(A+A)

= A+B ·C

Exercício 2Obtenha a tabela de verdade para cada uma das seguintes funções booleanas.

a) F (A,B,C) = (A+B)·(A+B + C)

b) F (X,Y, Z) = X ·Y +X ·Y ·Z

a) Se um termo soma é 0 então a função também é 0. Assim:

• se A=0 e B=1, então F=0;• se A=0 e B=0 e C=1, então F=0.

Desta forma identificam-se as combinações das variáveis, isto é, as linhas da tabela de verdadeonde F=0, tal como apresentado. Nas restantes situações F=1.

A B C F0 0 0 10 0 1 0 ←− A+B + C

0 1 0 0 ←− A+B

0 1 1 0 ←− A+B1 0 0 11 0 1 11 1 0 11 1 1 1

b) Se um termo produto é 1 então a função também é 1. Assim:

• se X=1 e Y=0, então F=1;• se X=0 e Y=1 e Z=0, então F=1.

Desta forma identificam-se as combinações das variáveis, isto é, as linhas da tabela de verdadeonde F=1, tal como apresentado. Nas restantes situações F=0.

X Y Z F0 0 0 00 0 1 00 1 0 1 ←− X ·Y ·Z0 1 1 01 0 0 1 ←− X ·Y1 0 1 1 ←− X ·Y1 1 0 01 1 1 0

Arquitetura e Organização de Computadores Pág. 19 de 100

Circuitos combinatórios — Exercícios resolvidos

Exercício 3Escreva uma expressão booleana para as funções lógicas representadas pelas tabelas deverdade indicadas.

x y f

0 0 10 1 01 0 01 1 1

a) x y z f

0 0 0 10 0 1 10 1 0 10 1 1 01 0 0 11 0 1 11 1 0 01 1 1 0

b)

A partir da tabela de verdade de uma função booleana podem retirar-se expressões algébricasna forma de uma soma de produtos ou na forma de um produto de somas.

Para a expressão na forma de uma soma de produtos identificam-se as linhas da tabela deverdade onde a função é 1 e forma-se um termo produto tal que nessa combinação das variáveisda função o valor do produto seja 1 (igual ao valor da função). A expressão da função obtém-sepela soma de todos os termos produto nestas condições.

Para a expressão na forma de um produto de somas identificam-se as linhas da tabela deverdade onde a função é 0 e forma-se um termo soma tal que nessa combinação das variáveis dafunção o valor da soma seja 0 (igual ao valor da função). A expressão da função obtém-se peloproduto de todos os termos soma nestas condições.

A partir destas expressões podem obter-se outras equivalentes por simplificação baseada emteoremas da álgebra de Boole.

a) Optando pela forma soma de produtos e procedendo da forma descrita, os termos produtoque definem a função são os indicados.

x y f0 0 1 −→ x·y0 1 01 0 01 1 1 −→ x·y

Logo, f(x, y) = x·y + x·y.

b) Optando pela forma produto de somas e procedendo da forma descrita, os termos soma quedefinem a função são os indicados.

Arquitetura e Organização de Computadores Pág. 20 de 100

Circuitos combinatórios — Exercícios resolvidos

x y z g0 0 0 10 0 1 10 1 0 10 1 1 0 −→ x+ y + z1 0 0 11 0 1 11 1 0 0 −→ x+ y + z1 1 1 0 −→ x+ y + z

Logo, g(x, y, z) = (x+ y + z)·(x+ y + z)·(x+ y + z).

Exercício 4Considere a função booleana F (X,Y, Z) com

F (X,Y, Z) = X ·Y ·Z +X ·Y ·Z +X · Y ·Z +X ·Y ·Z +X ·Y ·Z +X ·Y ·Z

a) Simplifique a expressão de F (X,Y, Z).

b) Construa a tabela de verdade da função.

c) Indique a expressão de F (X,Y, Z) na forma de um produto de somas.

d) Obtenha um circuito lógico que realiza a função F (X,Y, Z), usando apenas portaslógicas do tipo NOR.

a) F (X,Y, Z) = X ·Y ·Z +X ·Y ·Z +X ·Y ·Z +X ·Y ·Z +X ·Y ·Z +X ·Y ·Z= X ·Y ·(Z + Z) +X ·Y ·Z +X ·Y ·(Z + Z) +X ·Y ·Z= X ·Y +X ·Y +X ·Y ·Z +X ·Y ·Z= Y +X ·Y ·Z +X ·Y ·Z= Y +X ·Z +X ·Z

b) Como a expressão de F está na forma de uma soma de produtos, cada termo produtoidentifica combinações das entradas X,Y, Z onde F = 1. Ao lado da tabela de verdadeindicam-se esses termos.

X Y Z F

0 0 0 1 ←− Y e X ·Z0 0 1 1 ←− Y

0 1 0 1 ←− X ·Z0 1 1 01 0 0 1 ←− Y

1 0 1 1 ←− Y e X ·Z1 1 0 01 1 1 1 ←− X ·Z

c) Na tabela de verdade identificam-se os termos soma para os quais F=0. São eles

X + Y + Z e X + Y + Z

Arquitetura e Organização de Computadores Pág. 21 de 100

Circuitos combinatórios — Exercícios resolvidos

resultandoF (X,Y, Z) = (X + Y + Z)·(X + Y + Z)

d) Considerando a expressão da função na forma de um produto de somas, pode obter-se umaexpressão equivalente apenas com somas lógicas negadas, cada uma das quais será realizadapor uma porta NOR no circuito lógico pretendido. A negação das variáveis pode tambémrealizar-se através de um NOR aplicando a variável a negar a ambas as entradas do NOR.

F (X,Y, Z) = (X + Y + Z)·(X + Y + Z) = X + Y + Z +X + Y + Z

O circuito resultante é:

F

X

Y

Z

Exercício 5O circuito da figura implementa uma função F (A,B,C).

F

1

C

A

B

a) Deduza uma expressão da função lógica realizada pelo circuito, indicando-a na formade um produto de somas.

b) Escreva F (A,B,C) como uma soma de produtos simplificada.

a) A expressão da função realizada pelo circuito lógico pode obter-se através das expressões queresultam da saída de cada porta lógica como funções das entradas do circuito.

F (A,B,C) = A·B ·(1⊕ C) +A·B= A·B ·C +A·B= A·B ·C ·A·B= (A+B + C)·(A+B)

b) F (A,B,C) = (A+B + C)·(A+B)

= A·A+A·B +A·B +B +A·C +B ·C= (A+A+ 1 + C)·B +A·C= B +A·C

Arquitetura e Organização de Computadores Pág. 22 de 100

Circuitos combinatórios — Exercícios resolvidos

Exercício 6Pretende-se projetar um circuito capaz de detetar se um número com 3 bits n2n1n0 apli-cado à sua entrada está compreendido entre 2 e 5 (inclusive). A saída do circuito é umafunção de 3 variáveis, G(n2, n1, n0), sendo G = 1 para os números nas condições indicadase G = 0 no caso contrário. Defina o comportamento do circuito que realiza G na formade uma tabela de verdade.

Para os números compreendidos entre 2 e 5, formados em binário por n2n1n0, G = 1. Paraos restantes G é 0. Assim resulta a tabela de verdade seguinte:

n2 n1 n0 G

0 0 0 00 0 1 00 1 0 10 1 1 11 0 0 11 0 1 11 1 0 01 1 1 0

Exercício 7A figura mostra um circuito, baseado num multiplexador de 8 para 1, que realiza umafunção F (W,X, Y, Z).

MUX8:1

D0

D1

D2

D3

D4

D5

D6

D7

S2

Y

Z

1

YW X

F

S1S0

0

a) Defina F (W,X, Y, Z) através de uma tabela de verdade.

b) Represente F (W,X, Y, Z) através de uma expressão algébrica.

a) As variáveis W , X e Y determinam a entrada do multiplexador que é selecionada. O valornela aplicado surge na saída do circuito. A tabela de verdade pretendida obtém-se conside-rando todas as combinações das variáveis e consequentes valores da função.

Arquitetura e Organização de Computadores Pág. 23 de 100

Circuitos combinatórios — Exercícios resolvidos

W X Y Z F

0 0 0 0 00 0 0 1 10 0 1 0 10 0 1 1 00 1 0 0 00 1 0 1 00 1 1 0 00 1 1 1 01 0 0 0 01 0 0 1 11 0 1 0 01 0 1 1 11 1 0 0 01 1 0 1 01 1 1 0 11 1 1 1 1

b) Considere-se a forma soma de produtos nesta resolução. Embora não seja requerido noenunciado vai proceder-se à simplificação da expressão.

F = W ·X ·Y ·Z +W ·X ·Y ·Z +W ·X ·Y ·Z +W ·X ·Y ·Z +W ·X ·Y ·Z +W ·X ·Y ·Z= W ·X ·Y ·Z +W ·X ·Y ·Z +W ·X ·Z ·(Y + Y ) +W ·X ·Y ·(Z + Z)

= W ·X ·Y ·Z +W ·X ·Y ·Z +W ·X ·Z +W ·X ·Y= X ·(Z ·(W ·Y +W ) +W ·Y ·Z) +W ·X ·Y= X ·(Y ·Z +W ·Z +W ·Y ·Z) +W ·X ·Y= X ·Y ·Z +W ·X ·Z +W ·X ·Y ·Z +W ·X ·Y

Exercício 8Seja a função booleana S = (A+B + C) · (A+B + C).

a) Represente S através de uma tabela de verdade.

b) Realize a função S recorrendo ao multiplexador de 8 para 1 da figura.

MUX8:1

D0D1D2D3D4D5D6D7

S2

Y

(MS B)

S1S0

Arquitetura e Organização de Computadores Pág. 24 de 100

Circuitos combinatórios — Exercícios resolvidos

A B C S

0 0 0 00 0 1 10 1 0 10 1 1 01 0 0 11 0 1 11 1 0 11 1 1 1

a) Efetuar as seguintes ligações:

D0 = 0, D1 = D2 = 1, D3 = 0,D4 = D5 = D6 = D7 = 1,S2 = A, S1 = B, S0 = C e Y = F .

b)

Exercício 9Pretende-se realizar um circuito capaz de comparar duas quantidades positivas A e B,representadas em binário com 2 bits cada uma (a1a0 e b1b0), e produzir duas saídas, X eY . A saída X deve ser 1 se e só se A = B, e a saída Y deve ser 1 se e só se A > B.

a) Construa uma tabela de verdade de X e Y como funções de a1, a0, b1 e b0.

b) Obtenha um circuito que realize a função Y .

c) Mostre como, com um mínimo de esforço, poderia acrescentar a este circuito umasaída Z que fosse 1 quando A < B.

d) Admitindo que tinha disponíveis vários circuitos como o descrito atrás, mostre comoos poderia utilizar para realizar a comparação de quantidades de 6 bits cada, isto é,de modo a detetar as situações de A = B e A > B quando A = a5a4a3a2a1a0 eB = b5b4b3b2b1b0.

a) a1 a0 b1 b0 X Y

0 0 0 0 1 00 0 0 1 0 00 0 1 0 0 00 0 1 1 0 00 1 0 0 0 10 1 0 1 1 00 1 1 0 0 00 1 1 1 0 01 0 0 0 0 11 0 0 1 0 11 0 1 0 1 01 0 1 1 0 01 1 0 0 0 11 1 0 1 0 11 1 1 0 0 11 1 1 1 1 0

Arquitetura e Organização de Computadores Pág. 25 de 100

Circuitos combinatórios — Exercícios propostos

b) Y = a1 ·a0 ·b1 ·b0 + a1 ·a0 ·b1 + a1 ·a0 ·b1 + a1 ·a0 ·b1 ·b0= a1 ·a0 ·b1 ·b0 + a1 ·b1 + a1 ·a0 ·b1 ·b0= a1 ·a0 ·b1 ·b0 + a1 ·(b1 + a0 ·b1 ·b0)

= a1 ·a0 ·b1 ·b0 + a1 ·(b1 + a0 ·b0)

= a1 ·b1 + a1 ·a0 ·b0 + a1 ·a0 ·b1 ·b0= a1 ·b1 +·a0 ·b0(a1 + a1 ·b1)

= a1 ·b1 +·a0 ·b0(a1 + b1)

= a1 ·b1 + a0 ·b1 ·b0 + a1 ·a0 ·b0

Desenhar o circuito a partir da expressão encontrada.

c) A função pretendida define-se comoZ = X ·Y

d) Usar 3 circuitos comparadores de 2 bits idênticos aos da alínea a), combinando as saídas daseguinte forma:

X = X1 ·X2 ·X3 e Y = Y3 +X3 ·Y2 +X3 ·X2 ·Y1em que:

• X1 é a saída X do comparador de a1a0 com b1b0;

• X2 é a saída X do comparador de a3a2 com b3b2;

• X3 é a saída X do comparador de a5a4 com b5b4;

• Y1, Y2 e Y3 são as saídas Y dos comparadores correspondentes.

3.2 Exercícios propostos

Exercício 10Simplifique algebricamente as seguintes funções booleanas utilizando teoremas da álgebra deBoole.

a) F (A,B,C,D,E) = A·B ·C + C ·D ·E +A·B +A·B ·C ·D·E +A·B ·D ·E + C ·D ·E.

b) F (A,B,C) = A+A·B +A·C.

c) G(A,B,C) = A·B ·C +A·B ·C +A·B ·C.

d) F (A,B,C,D) = B ·C ·D +A·(C +B) +A·C ·D +A·B ·C ·D.

e) F (W,X, Y, Z) = W ·(X + Y ·(Z +W )).

f) F (A,B,C,D) = A·B ·C +B ·C ·D +A·B ·C ·D +A·B ·C ·D.

Arquitetura e Organização de Computadores Pág. 26 de 100

Circuitos combinatórios — Exercícios propostos

Exercício 11Obtenha a tabela de verdade para cada uma das seguintes funções booleanas.

a) F (A,B,C) = A·B +A·C.

b) G(X,Y, Z) = (X + Z)·(X + Y + Z).

c) F (W,X, Y, Z) = W ·X ·(Y + Z).

Exercício 12Considere a função F (X,Y, Z) = X ·Y +X ·Y ·Z +X ·Z.

a) Indique a respetiva tabela de verdade.

b) Escreva F (X,Y, Z) como um produto de somas.

c) Desenhe o circuito lógico correspondente.

Exercício 13Considere o circuito lógico apresentado na figura.

a) Deduza a expressão booleana simplificada correspondente à saída Y do circuito.

b) Mostre que a saída Z pode ser definida por Z(A,B,C) = B + C.

Exercício 14

Considere a função booleana F (A,B,C) = A+B + C +A·B ·C.

a) Indique a expressão de F (A,B,C) como uma soma de produtos simplificada.

b) Construa a tabela de verdade da função F (A,B,C).

c) Obtenha um circuito lógico que realize a função F (A,B,C).

Exercício 15Considere as seguintes funções booleanas:

F = X ·Y +X ·Y ·Z e G = (A+B + C)·(A+B +D)·(B + C +D)·(A+B + C +D).

a) Represente F (X,Y, Z) através de uma tabela de verdade e obtenha uma expressão na formade um produto de somas.

Arquitetura e Organização de Computadores Pág. 27 de 100

Circuitos combinatórios — Exercícios propostos

b) Represente G(A,B,C,D) através de uma tabela de verdade e obtenha uma expressão naforma de uma soma de produtos (não simplificada).

Exercício 16Seja a função booleana G(A,B,C) = A·C +B·A·C +B·C ·A. Exprima G(A,B,C) na forma deum produto de somas simplificado.

Exercício 17A figura seguinte mostra um circuito que realiza uma função G(X,Y, S). Além de portas lógicas,o circuito inclui um bloco, M, que realiza a função F (A,B, S) definida por: F = A se S = 0 eF = B se S = 1.

M

X

YA

B

S

F(A, B, S)

G(X, Y, S)

a) Exprima a função F numa tabela de verdade.

b) Indique uma expressão simplificada para F (A,B, S).

c) O circuito que realiza a função F é um multiplexador (multiplexer) de 2 para 1. Mostrecomo é constituído.

d) Encontre uma expressão simplificada do tipo soma de produtos para a função G(X,Y, S)realizada pelo circuito.

e) Mostre que o circuito seguinte, usando apenas portas NAND, realiza a função G.

Y

X

S G

Exercício 18Considere um circuito que apresenta na saída S o valor lógico 1 sempre que na sua entrada onúmero positivo de 4 bits, A3A2A1A0, é maior que 5 e múltiplo de 4.

a) Construa a tabela de verdade da função S(A3, A2, A1, A0).

b) Obtenha uma expressão para S(A3, A2, A1, A0) e simplifique-a.

Arquitetura e Organização de Computadores Pág. 28 de 100

Circuitos combinatórios — Exercícios propostos

Exercício 19Um circuito elementar utilizado na construção de circuitos digitais para aritmética binária é osomador completo (full-adder) representado na figura. O somador tem 2 saídas Co e S querepresentam em binário a soma dos valores (0 ou 1) presentes nas entradas A, B e Ci.

A B

CiCo

S

a) Construa a tabela de verdade correspondente às funções S(A,B,Ci) e Co(A,B,Ci).

b) Escreva a expressão das funções S(A,B,Ci) e Co(A,B,Ci) na forma de uma soma de pro-dutos.

c) Verifique que o circuito lógico da figura seguinte realiza as funções S(A,B,Ci) e Co(A,B,Ci).

A

B

Ci

Co

S

d) Considere agora um somador de 4 bits, constituído por 4 somadores completos, como mostraa figura.

A3

CiCo

A B

CiCo

S

A B

CiCo

S

A B

CiCo

S

A B

CiCo

S

B3

S3

A2 B2 A1 B1 A0 B0

S2 S1 S0

w1w2w3

Identifique na figura o valor de cada um dos sinais admitindo que os valores a somar, repre-sentando números positivos, são A = A3A2A1A0 = 1010 e B = B3B2B1B0 = 1110.

Exercício 20Pretende-se construir um circuito combinatório para comparar dois números de 2 bits, sem sinal,A = A1A0 e B = B1B0. A saída MAIOR é 1 quando A for maior do que B e 0 no caso contrário.

A1

MAIOR

A0

B1

B0

A>B?

Arquitetura e Organização de Computadores Pág. 29 de 100

Circuitos combinatórios — Exercícios propostos

a) Expresse a função do circuito numa tabela de verdade.

b) Escreva uma expressão da função MAIOR(A1, A0, B1, B0).

Exercício 21O circuito da figura contém um comparador de magnitude de 2 bits e 2 multiplexadores de 2 para1. As entradas do circuito formam dois números positivos, de 2 bits, A = A1A0 e B = B1B0.As saídas definem um número, também com 2 bits, M = M1M0. Analise o circuito e identifiquea sua funcionalidade.

A1

A0

B1

B0

A>B

COMP2

M1

S

MUX2_1

I1

I0

Y M0

S

MUX2_1

I1

I0

Y

Exercício 22Um multiplexador com n entradas de seleção pode ser usado para implementar qualquer funçãológica de n variáveis. Na figura mostra-se o símbolo de um multiplexador de 4 para 1, o qualpossui 2 entradas de seleção.

MUX4:1

D0

D1

D2

D3

Y

S1S0

a) Mostre como implementar o produto lógico de duas variáveis recorrendo ao multiplexador.

b) Realize a função F (X,Y ) = X ·Y +X ·Y com o multiplexador apresentado.

Arquitetura e Organização de Computadores Pág. 30 de 100

Circuitos combinatórios — Exercícios propostos

c) Verifique, exemplificando, que é igualmente possível implementar funções de três variáveis.Sugestão: represente uma função de 3 variáveis através de uma tabela de verdade e, paracada combinação das variáveis, relacione o valor da função com uma dessas variáveis.

Exercício 23A figura mostra um circuito constituído por um descodificador binário de 2 para 4 e um conjuntode 3 lâmpadas. O estado das lâmpadas é controlado pelas entradas A e B do circuito, ou seja,Lvm, Llj e Lvr são funções de A e B. Admita que para ligar uma lâmpada é necessário que asaída do descodificador que a controla tenha o valor lógico 1.

DEC2_4

I1

I0

Y0

Y1

Y2

Y3

Lvm

Lvr

Llj

A

B

a) Indique o estado de cada lâmpada se AB = 01 e AB = 11.

b) Determine o valor das entradas de modo a ligar, simultaneamente, as lâmpadas verde (Lvr =1) e laranja (Llj = 1).

Arquitetura e Organização de Computadores Pág. 31 de 100

4 Circuitos sequenciais

4.1 Exercícios resolvidos

Exercício 1Considere o seguinte circuito com uma entrada X e uma saída Y .

X

CLK

D Q

Y

CLKCLK

D Q

a) Desenhe no diagrama seguinte a evolução temporal das saídas dos flip-flops (Q1 e Q0),assim como da saída Y , sabendo que a entrada X evolui da forma representada. Nota:considere que no instante inicial Q1 e Q0 têm o valor lógico 0.

b) Admitindo que o período do sinal de relógio é 20 ns, indique ao fim de quanto tempoa saída Y passa de 0 a 1 pela primeira vez.

a) Como inicialmente Q0 = 0 e Q1 = 0, nas entradas dos flip-flops vão estar os valores D0 = 0 eD1 = 1, uma vez que X = 0. Ao ocorrer a primeira transição do sinal de relógio são estes osvalores capturados pelos flip-flops, aparecendo nas saídas respetivas. Na próxima transição,o estado das saídas e X determinam os novos valores que os flip-flops vão apresentar. Assimse completam as formas de onda apresentadas.

Arquitetura e Organização de Computadores Pág. 32 de 100

Circuitos sequenciais — Exercícios resolvidos

CK

X

Q1

Q0

Y

b) Considerando T = 20ns, verifica-se pelo resultado da alínea anterior que Y transita de 0para 1 ao fim de 2,5× T =50 ns.

Exercício 2Considere o seguinte circuito sequencial, constituído por dois flip-flops e um multiplexador.Os flip-flops são sensíveis à transição ascendente do sinal de relógio (CLK) e o seu estadoinicial é 0.

CLK

D Q

CLK

OUTIN

CLK

D QX

I0

YI1

S

1

MUX2_1

Assumindo a sequência de valores da entrada do circuito (IN) indicada na figura seguinte,apresente a forma de onda dos sinais X e OUT.

CLK

IN

X

OUT

Inicialmente, X e OUT apresentam o valor 0. Sendo a entrada de seleção do multiplexador 0, ovalor que surge na sua saída é 1, referente à entrada I0. Como IN = 0 e Y = 1 quando ocorrea primeira transição do sinal de relógio, então X e OUT passam a assumir os valores 0 e 1,respetivamente. A análise do sucedido para as restantes transições segue o mesmo raciocínio,levando ao resultado apresentado na figura seguinte.

Arquitetura e Organização de Computadores Pág. 33 de 100

Circuitos sequenciais — Exercícios resolvidos

CLK

IN

X

OUT

Exercício 3Considere o circuito, composto por um registo de 4 bits e um multiplexador com duasentradas de 4 bits. Admita que as entradas enable e reset do registo são ativadas pelovalor lógico 1.

D[3:0]

Q[3:0]

CLK

REG_4bits

enable

reset

CLK

I0[3:0]

Y[3:0]

S

MUX_2

I1[3:0]

4

4

4

en

rst

IN

D

OUT4

Nas alíneas seguintes, considere em cada transição ativa do sinal de relógio o valor dasentradas apresentadas em cada tabela. Determine o valor da saída OUT após cada umadas transições assinaladas.

Transição D en rst

1 0110 1 02 0100 1 13 0100 0 04 1101 1 0

a) Transição IN sel en rst

1 1001 1 1 02 1111 1 1 03 0101 0 1 04 1000 1 0 05 1000 1 1 06 1111 1 1 17 0101 0 1 08 0000 1 1 09 0001 1 1 0

b)

a) Os sinais considerados só envolvem o registo de 4 bits. Para cada transição ativa do sinal derelógio é necessário ter em consideração que a saída do registo assume o valor presente na en-trada D se a entrada de habilitação (enable) estiver ativa (en = 1), permanecendo inalteradoaté à próxima transição. Caso en seja 0, a saída mantém o valor anterior. Relativamente à

Arquitetura e Organização de Computadores Pág. 34 de 100

Circuitos sequenciais — Exercícios resolvidos

entrada reset do registo, quando ativo (rst = 1) coloca a saída em 0000, independentementedo valor das restantes entradas.

Aplicando estas considerações à sequência de entradas dada, obtém-se a saída OUT como semostra na tabela seguinte.

Transição (CLK) D en rst OUT

1 0110 1 0 01102 0100 1 1 00003 0010 0 0 00004 1101 1 0 1101

b) Além do que foi descrito na análise anterior, há agora que ter em consideração o multiplexa-dor. Observando a forma como está a ser usado, conclui-se que o valor aplicado na entradado registo provém da entrada IN , quando sel = 1, ou da saída OUT do registo, quandosel = 0.

Aplicando estas considerações à sequência de entradas dada, obtém-se a saída OUT como semostra na tabela seguinte.

Transição (CLK) IN sel en rst OUT

1 1001 1 1 0 10012 1111 1 1 0 11113 0101 0 1 0 11114 1000 1 0 0 11115 1000 1 1 0 10006 1111 1 1 1 00007 0101 0 1 0 00008 0000 1 1 0 00009 0001 1 1 0 0001

Arquitetura e Organização de Computadores Pág. 35 de 100

Circuitos sequenciais — Exercícios resolvidos

Exercício 4A figura representa um circuito sequencial baseado num contador de 4 bits.

CLK

EN

CLK

QAENQB

QC

QD

CONT4

(MSB)

OUT

Q3

Q2

Q0Q1

a) Desenhe as formas de onda das saídas do contador (Q3, Q2, Q1 e Q0) e do circuitocompleto (OUT).

b) Indique a sequência de estados ocorridos, numerando-os em decimal.

c) Considere agora que o contador possui uma entrada de reset (ativa a 1), acionada comomostra a figura seguinte. Determine a sequência de estados da saída do contador.

CLK

EN

CLK

QAENQB

QC

QD

CONT4

(MSB)

OUTRESET

a) O circuito apresentado é constituído por um contador de 4 bits. Considerando que inici-almente as suas saídas são nulas, a cada transição do sinal de relógio o valor das saídas éincrementado, resultando a representação das formas de onda mostrada na figura seguinte.

C KL

Q0

Q1

Q2

Q3

OUT

b) Sequência de estados (valores resultantes de Q3Q2Q1Q0):

0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 0, · · ·

Arquitetura e Organização de Computadores Pág. 36 de 100

Circuitos sequenciais — Exercícios resolvidos

c) No estado QDQCQBQA = 0100 a entrada de reset fica ativa. Admitindo-o síncrono, napróxima transição do sinal de relógio o estado do contador passa para 0000. A sequência deestados resultante é: 0, 1, 2, 3, 4, 0, · · · .

Exercício 5Considere os sistemas de memória externa apresentados na figura seguinte.

A[15:0]

RAM1 RAM2

A[11:0] A[12:0]

CS CS

D[7:0] D[7:0]

8 bits 8 bits

8 bits

A[14]

A[13]

A[15]

A[15]

A[12]

A[13]

A[14]

& &

(a)

RAM1 RAM2

A[12:0]A[15:0]

A[13:0]

CS CS

D[7:0] D[7:0]

8 bits

8 bits

8 bits

A[15]

A[15]

A[13]

&

(b)

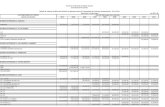

a) Determine a capacidade de cada circuito de memória.

b) Elabore o mapa de memória de cada sistema. Indique, justificando, se a descodificaçãode memória é total ou parcial.

c) Para cada um dos seguintes endereços, indique o componente, ou seja, o circuito dememória, afetado: B7FFH, 1000H, E7AAHe 8000H.

a) Obtém-se a capacidade de um circuito de memória multiplicando o número de posições pelonúmero de bits por posição. O número de bits por posição é igual ao número de bits do portode dados D[]. Todos os circuitos deste problema têm um porto de dados de 8 bits (1 byte).

O número de posições é determinado pela dimensão do porto de endereços A[]. Para portosde N bits, existem 2N posições.

Assim, para a figura (a) temos:

• RAM1: 212 × 8 bits = 22 × 210 × 8 bits = 4× 210 byte = 4KiB

• RAM2: 213 × 8 bits = 8KiB

Para a figura (b) temos:

• RAM1: 213 × 8 bits = 8KiB

• RAM2: 214 × 8 bits = 16KiB

b) O mapa de memória indica, para cada endereço possível, qual o circuito que armazena osdados correspondentes. Em ambas as figuras, o barramento de endereços do CPU tem 16bits (A[15:0]). Portanto, o espaço de endereçamento tem 216 posições (de 1 byte, nestecaso), i.e., 64KB. A gama de endereços vai de 0000H a FFFFH.

Arquitetura e Organização de Computadores Pág. 37 de 100

Circuitos sequenciais — Exercícios resolvidos

Os endereços mapeados em cada circuito podem ser determinados por análise das condiçõesem que o circuito está habilitado, i.e., para que endereços é que se tem CS=1.

Para a figura (a) temos:

• RAM1: CS = A15 ·A14 ·A13 ·A12 = 1.Esta condição só é satisfeita se A15 = 1, A14 = 1, A13 = 1, A12 = 0.Logo, os endereços mapeadas na RAM1 têm o formato

1110 XXXX XXXX XXXXem que X indica que o bit correspondente tanto pode ser 0 como 1. Os endereços comeste formato estão na gama:

1110 0000 0000 0000 a 1110 1111 1111 1111.Em hexadecimal, a gama é E000H–EFFFH.Como todos os bits do endereço são usados (A15−A12 na definição de CS; os restantesna ligação ao porto de endereços de RAM1), trata-se de descodificação total.

• RAM2: CS = A15 ·A14 ·A13 = 1.Esta condição só é satisfeita se A15 = 1, A14 = 0, A13 = 0.Logo, os endereços mapeadas na RAM2 têm o formato

100X XXXX XXXX XXXX.Os endereços com este formato estão na gama:

1000 0000 0000 0000 a 1001 1111 1111 1111.Em hexadecimal, a gama é 8000H–9FFFH.Trata-se igualmente de descodificação total.

O mapa de memória para o sistema da figura (a) é o seguinte:

Gama (hex) Dispositivo0000–7FFF –-8000–9FFF RAM2A000–DFFF –-E000–EFFF RAM1F000–FFFF –-

A análise do sistema da figura (b) faz-se de forma análoga.

• RAM1: CS = A15 ·A13 = 1. Esta condição só é satisfeita se A15 = 1, A13 = 0.Logo, os endereços mapeadas na RAM1 têm o formato

1?0X XXXX XXXX XXXX.O símbolo ? indica que o bit correspondente não é usado na descodificação. Portanto,trata-se de descodificação parcial.Neste caso particular, dois endereços que difiram apenas no bit A14 têm o mesmo efeitoem termos de acesso a memória: os dois endereços diferentes são mapeados no mesmaposição física de memória. Temos, portanto, duas gamas de endereços equivalentes, queapenas diferem no valor de A14. Para A14 = 0 a gama é:

1000 0000 0000 0000 a 1001 1111 1111 1111.Em hexadecimal, a gama é 8000H–9FFFH.Para A14 = 1 a gama é:

Arquitetura e Organização de Computadores Pág. 38 de 100

Circuitos sequenciais — Exercícios propostos

1100 0000 0000 0000 a 1101 1111 1111 1111.Em hexadecimal, a gama é C000H–DFFFH.As duas gamas são mapeadas de forma sobreposta na RAM1. Por exemplo, os endereços8000H e C000H referem-se ambos à primeira posição física do circuito RAM1. A memóriadisponível não aumenta por ser usada descodificação parcial.

• O circuito RAM2 também é usado com descodificação parcial. Os endereços correspon-dentes têm o formato

0?XX XXXX XXXX XXXX,a que correspondem as gamas 0000H–3FFFH e 4000H–7FFFH.

O mapa de memória para o sistema da figura (b) é o seguinte:

Gama (hex) Dispositivo

0000–3FFF RAM2 (*)4000–7FFF RAM2 (*)8000–9FFF RAM1 (**)A000–BFFF –-C000–DFFF RAM1 (**)E000–FFFF –-

Os asteriscos assinalam gamas fisicamente sobrepostas.

c) Para determinar os componentes usados basta consultar os mapas de memória obtidos naalínea anterior. Os resultados são os seguintes:

Endereço Figura (a) Figura (b)B7FF –- –-1000 –- RAM2E7AA RAM1 –-8000 RAM2 RAM1

4.2 Exercícios propostos

Exercício 6Assuma que no circuito seguinte os flip-flops do tipo D são sensíveis ao flanco ascendente dosinal de relógio e que inicialmente as saídas são nulas.

CLK

D Q

Q

CLK

QD

CLK

D Q

Q

X

Represente a forma de onda da saída Q em resposta à entrada D representada na figura.Sugestão: comece por verificar qual o valor de X após cada transição do sinal de relógio.

Arquitetura e Organização de Computadores Pág. 39 de 100

Circuitos sequenciais — Exercícios propostos

CLK

D

X

Q

Exercício 7Considere o seguinte circuito sequencial, constituído por portas lógicas e um flip-flop do tipo D,sensível ao flanco ascendente do sinal de relógio, em que no início Q = 0.

CLK

D Q

Q

J

CLK

QK

Q

a) Indique a expressão da função lógica D(J,K,Q) à entrada do flip-flop.

b) Considerando os valores das entradas J e K apresentados na figura seguinte, obtenha o valorda saída Q do circuito.

CLK

J

K

Q

Exercício 8Considere o circuito sequencial da figura seguinte.

Arquitetura e Organização de Computadores Pág. 40 de 100

Circuitos sequenciais — Exercícios propostos

D

CLK

Q

D0

EN

CLK

D

CLK

Q

D1

Q0

Q1

a) Escreva a expressão das entradas D0 e D1 dos flip-flops.

b) Represente as formas de onda correspondentes aos sinais Q0 e Q1, assumindo que o estadoinicial dos flip-flops é “00” e que EN=1.

c) Mostre qual o estado do circuito após 4 transições consecutivas do sinal de relógio (CLK).

Exercício 9Considere o seguinte circuito, composto por um flip-flop e uma porta XOR (ou-exclusivo).

CLK

D Q

CLK

TX

a) Assumindo que o estado inicial do flip-flop é 0, determine a sequência de valores na saída Tse na entrada X ocorrer a sequência 0110001001111100 (um bit a cada ciclo do relógio).

b) Ao circuito anterior foi acrescentado um contador síncrono de 4 bits, tal como representadona figura seguinte. Identifique a relação entre as saídas Q3Q2Q1Q0 do contador e a entradaX do circuito.

CLK

D Q

CLK

TX

CLK

QAENQB

QC

QD

CONT4

Q3

Q2

Q0Q1

(MSB)

Arquitetura e Organização de Computadores Pág. 41 de 100

Circuitos sequenciais — Exercícios propostos

Exercício 10A figura mostra a constituição de um banco de registos.

Além dos 8 registos de 4 bits, fazem parte do circuito um descodificador de 3 para 8 e ummultiplexador de 8 (conteúdos de 4 bits) para 1. A entrada DIN representa o valor de 4 bits aescrever num dos 8 registos, endereçado (identificado) por ADDR. A escrita ocorre se WRITE=1.A leitura de um registo é feita endereçando o registo pretendido, surgindo o valor na saída DOUT.As operações de escrita são síncronas com o sinal de relógio.

a) Expresse a capacidade de armazenamento do banco de registos em bytes.

b) Explique o que garante escrever um conteúdo num (e um só) determinado registo.

c) Admita que o conteúdo inicial dos registos é “0000” e que os valores das entradas são:DIN=1111, ADDR=001 e WRITE=1. Descreva que alterações ocorrem no circuito apósuma transição do sinal de relógio.

d) Explique a utilidade das entradas enable e reset dos registos.

e) Descreva a função desempenhada pelo descodificador de 3 para 8 e pelo multiplexador de 8para 1, no contexto da sua utilização no banco de registos.

f) Mostre que alteração seria necessária efetuar para que fosse possível ler, simultaneamente, oconteúdo de dois registos diferentes, apresentando-o nas saídas DOUT1 e DOUT2.

Exercício 11Um sistema de memória é constituído por uma memória RAM e uma memória ROM. O barra-mento de endereços possui 16 bits e o barramento de dados é de 8 bits. A figura seguinte mostrao correspondente diagrama de blocos, onde CS representa o sinal de chip select das memórias.

Arquitetura e Organização de Computadores Pág. 42 de 100

Circuitos sequenciais — Exercícios propostos

CPU

A[15:0]16

RAM

D[7:0] 8

A[11:0]

D[7:0]

CS

A[11:0]

A15

A13

A14

ADDRESS

DATA

ROM

A[10:0]

D[7:0]

CS

A[10:0]

?

a) Determine o intervalo de endereços a que a RAM responde e justifique se a descodificaçãode endereços é total ou parcial.

b) Considere que a primeira posição da memória ROM tem o endereço 0xC800 e que o endereçode cada posição é único. Calcule o endereço da última posição da ROM.

c) Apresente o circuito de descodificação de endereços da ROM considerando as condições daalínea anterior.

Exercício 12Um processador dispõe de um espaço de endereçamento de 64KiB e de um barramento de dadoscom 8 linhas. O seu mapa de memória é o seguinte:

Gama Dispositivo

0x0000-0x3FFF ROM10x4000-0x7FFF RAM10x8000-0xCFFF -0xD000-0xDFFF RAM20xE000-0xFFFF -

a) Determine as dimensões de cada um dos dispositivos de memória.

b) Determine as equações lógicas dos circuitos de descodificação de endereços (descodificaçãototal).

c) Apresente o diagrama de blocos do sistema de memória com descodificação de endereços.

Arquitetura e Organização de Computadores Pág. 43 de 100

5 Desempenho

Alguns destes exercícios são extraídos ou adaptados do livro “Computer Organization and Design– The Hardware/Software Interface”, D. Hennessy e J. Patterson, 4a edição.

5.1 Exercícios resolvidos

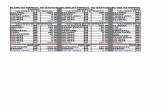

Exercício 1Um computador possui três classes de instruções, A, B e C. O CPI de cada uma delas é,respetivamente, 1, 2 e 3. Um projetista está a implementar um compilador e precisa deescolher uma de duas sequências de instruções a usar nesse computador. Dessas sequênciasé conhecido o número de instruções de cada classe, conforme mostra a tabela seguinte.

Sequência de instruções No de instruções por classeA B C

1 2 1 22 4 1 1

a) Determine em qual das duas sequências de instruções é executado o maior número deinstruções.

b) Mostre qual das sequências é executada de forma mais rápida.

c) Calcule o valor do CPI para cada sequência.

a) Na sequência 1 são executadas 2 + 1 + 2 = 5 instruções e na sequência 2 são executadas4 + 1 + 1 = 6 instruções. É pois na sequência 2 que são executadas mais instruções.

b) O número de ciclos é dado por

Nciclos =∑i

Ni × CPIi

onde Ni se refere ao número de instruções da classe i e CPIi é o número de ciclos por instruçãodessa classe.

Sequência 1: Nciclos = 2× 1 + 1× 2 + 2× 3 = 10

Sequência 2: Nciclos = 4× 1 + 1× 2 + 1× 3 = 9

A sequência 2 é a mais rápida, porque é executada em menos ciclos de relógio.

Arquitetura e Organização de Computadores Pág. 44 de 100

Desempenho — Exercícios resolvidos

c)

CPI =Nciclos

Ninst

Sequência 1: CPI = 10/5 = 2

Sequência 2: CPI = 9/6 = 1,5

Exercício 2Considere um computador com três classes de instruções, A, B e C, para as quais o valorde CPI é 1, 2 e 3, respetivamente. Para ser executado nesse computador, um programa éobtido através de dois compiladores distintos, originando o número de instruções de cadaclasse indicado na tabela.

Sequência de instruções No de instruções por classeA B C

Compilador 1 5× 109 1× 109 1× 109

Compilador 2 10× 109 1× 109 1× 109

Assuma que o computador funciona a 500MHz.

a) Indique a sequência que é executada em menos tempo.

b) Determine a qual das sequências de instruções corresponde o maior valor de MIPS(milhões de instruções por segundo).

a) O tempo de execução é dado por

texec =Nciclos

fCLK

sendo o número de ciclos de relógio determinado por

Nciclos =∑i

Ni × CPIi

Então, o tempo de execução da sequência de instruções obtida por cada compilador é

texec_C1 =(5× 1 + 1× 2 + 1× 3)× 109

500× 106=

10× 109

500× 106= 20 s

e

texec_C2 =(10× 1 + 1× 2 + 1× 3)× 109

500× 106=

15× 109

500× 106= 30 s

Atendendo aos tempos de execução calculados, conclui-se que o compilador 1 gera o programamais rápido.

b)

MIPS =Ninstr

texec × 106

Portanto,

MIPS1 =(5 + 1 + 1)× 109

20× 106= 350

Arquitetura e Organização de Computadores Pág. 45 de 100

Desempenho — Exercícios resolvidos

e

MIPS2 =(10 + 1 + 1)× 109

30× 106= 400

Daqui se conclui que o compilador 2 proporciona uma taxa de execução de instruções superior.

Exercício 3A execução de um programa num computador A, o qual funciona com um sinal de relógiode 2GHz, demora 10 s. Um computador B que está a ser desenvolvido é capaz de executaro mesmo programa em 6 s. Este computador B pode atingir uma frequência de relógiosuperior à do computador A, embora consuma 1,2 vezes mais ciclos de relógio do que ocomputador A a executar o referido programa. Determine a frequência do sinal de relógioa que B pode funcionar.

O tempo de execução de um programa com Ninstr instruções é dado por

texec = Ninstr × CPI× TCLK

A razão dos tempos de execução no computador A e no computador B é

texec_A

texec_B=

Ninstr × CPIA × fCLK_B

Ninstr × CPIB × fCLK_A=

10

6

Como CPIB = 1,2×CPIA, então resulta fCLK_B = fCLK_A× 1,2× 106 = 2× fCLK_A, conclui-se

que fCLK_B = 4GHz.

Exercício 4Considere dois computadores A e B que possuem o mesmo conjunto de instruções. Operíodo do sinal de relógio dos computadores A e B é 250 ps e 500 ps, respetivamente, e onúmero de ciclos de relógio consumidos por instrução (CPI) é 2 no computador A e 1,2 nocomputador B, respetivamente. Mostre qual dos computadores é o mais rápido a executarum programa.

texecA = Ninstr × 2× 250 = 500×Ninstr ps

etexecB = Ninstr × 1,2× 500 = 600×Ninstr ps

Então,texecBtexecA

=6

5= 1,2

O computador A é o mais rápido.

Arquitetura e Organização de Computadores Pág. 46 de 100

Desempenho — Exercícios resolvidos

Exercício 5Um dado programa é executado em dois computadores diferentes, A e B, tendo-se obtidoos seguintes indicadores:

Indicador A B

No de instruções 107 8× 106

Frequência 4GHz 4GHzCPI 1 1,1

a) Indique qual o computador com maior valor de MIPS.

b) Indique qual o computador mais rápido.

a)

MIPS =Ninstr

texec × 106=

Ninstr

Ninstr × CPI× TCLK × 106=

fCLK

CPI× 106

Logo,

MIPSA =4× 109

1× 106= 4× 103

e

MIPSB =4× 109

1,1× 106≈ 3636

A é o computador com maior valor de MIPS.

b)

texec = Ninstr × CPI× TCLK =Ninstr

MIPS× 106

texecA =107

4× 103 × 106= 2,5ms

texecB =8× 106

3636× 106≈ 2,2ms

B é o computador mais rápido.

Exercício 6Para um dado programa foram obtidas as seguintes medidas:

• Ocorrência de operações de vírgula flutuante (VFL) (exceto raiz quadrada): 25%• Ocorrência da operação de raiz quadrada: 2%• CPI médio de operações em VFL: 4,0• CPI de raiz quadrada: 20• CPI médio para outras instruções: 1,33

Considere duas alternativas para melhorar o desempenho: reduzir o CPI da operação deraiz quadrada para 2 ou baixar o CPI de todas as instruções de VFL para 2,5. Compareas duas alternativas usando a equação de desempenho do CPU.

Arquitetura e Organização de Computadores Pág. 47 de 100

Desempenho — Exercícios resolvidos

O número de instruções e a frequência do relógio do computador continuam a ser os mesmosnas duas alternativas. Basta por isso comparar os valores de CPI.

CPI1 = 0,25× 4 + 0,02× 2 + (1− 0,25− 0,02)× 1,33 ≈ 2,01

CPI2 = 0,25× 2,5 + 0,02× 20 + (1− 0,25− 0,02)× 1,33 ≈ 2,00

Embora os valores sejam muito próximos, na segunda alternativa (“... baixar o CPI de todas asinstruções de VFL para 2,5”) o tempo de execução é menor, ou seja, o desempenho é superior.

Exercício 7Um processador executa um programa em que 30% do tempo de execução é gasto emadições de vírgula flutuante, 25% em multiplicações de vírgula flutuante e 10% em divisõesde vírgula flutuante. Para a nova geração desse processador, a equipa de projeto propõetrês aperfeiçoamentos possíveis na unidade de vírgula flutuante, consistindo em tornar o:

1. somador duas vezes mais rápido;

2. multiplicador três vezes mais rápido;

3. divisor dez vezes mais rápido.

Indique qual destas alternativas poderá proporcionar o maior aumento de desempenho.

A lei de Amdahl pode ser expressa por

stotal(f) =1

(1− f) + fs

onde f representa a fração de tempo gasto na execução da parte melhorada e s traduz o aumentode rapidez dessa parte.

A aplicação da lei de Amdahl às três situações descritas permite pois quantificar o aumentode desempenho:

1. f = 0,3 e s = 2 → stotal(f) =1

0,7+0,3/2 = 1,18

2. f = 0,25 e s = 3 → stotal(f) =1

0,75+0,25/3 = 1,20

3. f = 0,1 e s = 10 → stotal(f) =1

0,9+0,1/10 = 1,10

O maior ganho de desempenho é obtido com a melhoria do multiplicador de vírgula flutuante(alternativa 2). Pode ainda concluir-se que tornar o divisor muito mais rápido leva ao menoraumento de desempenho devido à baixa ocorrência de divisões em vírgula flutuante (10%). Naverdade, mesmo tornando o divisor infinitamente mais rápido, o speed-up obtido seria 1,11.

Arquitetura e Organização de Computadores Pág. 48 de 100

Desempenho — Exercícios propostos

Exercício 8A execução de um programa num computador demora 1000 s, sendo 75% do tempo gastoem multiplicações e divisões. Pretende-se remodelar o computador com hardware maisrápido para a realização das operações de multiplicação e divisão. Calcule quanto maisrápidas devem ser as operações de multiplicação e divisão para que o programa seja:

três vezes mais rápido;a) quatro vezes mais rápido.b)

a) Aplicando a lei de Amdahl, o aumento de rapidez do programa é dado por

stotal(f) =1

(1− f) +f

s

onde f representa a fração de tempo gasto na execução da parte melhorada e s traduz oaumento de rapidez dessa parte. Assim,

3 =1

(1− 0,75) +0,75

s

=1

1

4+

3

4× s

=4× s

s+ 3

resultando3× s+ 9 = 4× s⇔ s = 9

isto é, as operações devem ser 9 vezes mais rápidas.

b) Da mesma forma, resulta

4 =1

(1− 0,75) +0,75

s

=1

1

4+

3

4× s

=4× s

s+ 3

e4× s+ 12 = 4× s

que não tem solução, concluindo-se ser impossível o programa ficar 4 vezes mais rápido.

5.2 Exercícios propostos

Exercício 9A tabela apresentada mostra a frequência de funcionamento de 3 processadores, o número deinstruções executadas em cada um deles e o respetivo tempo de execução.

Processador FCLK (GHz) No de instruções Tempo (s)

P1 2 20× 109 7P2 1,5 30× 109 10P3 3 90× 109 9

Arquitetura e Organização de Computadores Pág. 49 de 100

Desempenho — Exercícios propostos

a) Calcule o número de instruções executadas por ciclo de relógio, por cada processador.

b) Calcule a frequência a que o processador P2 deve funcionar para que o tempo de execuçãodas instruções seja igual ao apresentado para P1.

c) Calcule o número de instruções a executar em P2 de modo a que o seu tempo de execuçãoseja igual ao de P3.

Exercício 10Considere que dois processadores distintos, P1 e P2, implementam o mesmo conjunto de instru-ções e que estas se podem enquadrar em quatro classes diferentes (A, B, C e D). A frequênciae o CPI por classe de instruções de cada implementação encontram-se na tabela.

Processador FCLK (GHz) CPI A CPI B CPI C CPI D

P1 1,5 1 2 3 4P2 2 2 2 2 2

a) Seja um programa com 1 milhão de instruções divididas pelas quatro classes da seguinteforma: 10% são da classe A, 20% são da classe B, 50% são da classe C e 20% são da classeD. Verifique qual dos processadores é mais rápido a executar o programa.

b) Calcule o CPI médio de cada processador.

c) Calcule o número de ciclos de relógio necessários à execução do programa em cada processa-dor.

Exercício 11Considere dois processadores, P1 e P2, que implementam de forma diferente o mesmo conjuntode instruções, composto por cinco classes de instruções. P1 funciona com um relógio de 4GHz eP2 funciona a 6GHz. O número médio de ciclos de relógio para cada classe de instruções é dadopela tabela que se segue.

Classe CPI de P1 CPI de P2

A 1 2B 2 2C 3 2D 4 4E 3 4

Pico de desempenho é definido como a cadência máxima a que um computador pode executar asequência de instruções mais favorável (para uma dada tarefa). Determinar o pico de desempenhode P1 e P2, expresso em instruções por segundo.

Exercício 12A tabela seguinte apresenta o número de operações em vírgula flutuante (VFL) executadas emtrês programas diferentes e o respetivo tempo de execução em três computadores A, B e C,distintos.

Arquitetura e Organização de Computadores Pág. 50 de 100

Desempenho — Exercícios propostos

Programa No operações VFLTempo de execução (s)

Comp. A Comp. B Comp. C1 5× 109 2 5 102 20× 109 20 20 203 40× 109 200 50 15

a) Mostre qual o computador mais rápido em termos do tempo total de execução.

b) Determine quantas vezes esse computador é mais rápido do que os outros dois.

Exercício 13A tabela mostra o número total de instruções executadas por um programa, bem como a suadistribuição por tipo.

Total Aritméticas Store Load Salto

700 500 50 100 50

a) Assuma que o tempo de execução das instruções aritméticas corresponde a 1 ciclo de relógio,loads e stores correspondem a 5 ciclos de relógio e as instruções de salto correspondem a 2ciclos de relógio. Calcule o tempo de execução do programa num processador a 2GHz.

b) Calcule o valor do CPI para o programa.

c) Se o número de instruções de load for reduzido para metade, quanto mais rápida é a execuçãodo programa e qual o valor do CPI?

Exercício 14Um computador A tem um CPI médio de 1,3 e funciona a 600MHz. Um outro computador,B, tem um CPI médio de 2,5 e funciona a 750MHz. Pretende-se executar um certo programaem ambos os computadores. Compilando esse programa para o computador A resultaram 105

instruções. Determine quantas instruções devem resultar compilando-o para o computador B,de modo que a execução do programa demore o mesmo tempo em ambos os computadores.

Exercício 15Um processador executa um programa constituído por vários tipos de instruções, entre as quaisexistem instruções de transferência de dados. Supondo que é possível melhorar o tempo deexecução das instruções de transferência de dados em 11 vezes, calcule a percentagem dessasinstruções de forma a conseguir-se melhorar o desempenho do processador em 5 vezes.

Exercício 16Medindo o tempo de acesso a disco verificou-se que 80% do tempo de execução de um deter-minado programa num computador era gasto em acessos ao disco. Substituindo o disco de talcomputador constatou-se que este era duas vezes mais rápido.

a) Calcule quanto melhorou o desempenho do computador.

b) Verifique qual a melhoria de desempenho que seria alcançada se o disco tivesse um tempo deacesso desprezável.

Arquitetura e Organização de Computadores Pág. 51 de 100

Desempenho — Exercícios propostos

Exercício 17Suponha que se pretende melhorar um computador acrescentando-lhe uma unidade vetorial. Umcálculo executado em modo vetorial é 10 vezes mais rápido que o normal.

a) Desenhe um gráfico que mostre o ganho de rapidez (speedup) em função da percentagem detempo de execução em modo vetorial (percentagem de vetorização).

b) Que percentagem de vetorização é necessária para se obter um ganho de rapidez de 2?

c) Considerar o caso da alínea anterior. Com a utilização da unidade vetorial, o computadordemora metade de tempo a realizar os cálculos. Em que percentagem desse novo tempo(mais curto) é que a unidade vetorial está a ser usada?

d) Que percentagem de vetorização é necessária para obter metade do máximo ganho de rapidezpossível?

e) Suponha que se determinou empiricamente que a percentagem de vetorização é de 70%. Osprojetistas de hardware acham que é possível duplicar o desempenho da unidade vetorial. Emalternativa, o grupo de compilação poderia tentar aumentar a utilização do modo vetorial,como forma de aumentar o desempenho. Que aumento da percentagem de vetorização (emrelação à situação atual) seria necessário para obter o mesmo resultado que a duplicação dodesempenho de hardware? Que alternativa é mais aconselhável?

Arquitetura e Organização de Computadores Pág. 52 de 100

6 Linguagem assembly

6.1 Sumário das instruções MIPS-32

Instruções do tipo R com opcode=0. Valor do campo funct em hexadecimal:

add:20 addu:21 and:24 jr:8 nor:27 or:25 mult:18 multu:19 mfhi:10slt:2A sltu:2B sll:0 srl:2 sub:22 subu:23 div:1A divu:1B mflo:12

Instruções do tipo I. Valor do campo opcode em hexadecimal:

addi:8 addiu:9 andi:C beq:4 bne:5 lbu:24 lhu:25 lui:Flw:23 ori:D slti:A sltiu:B sb:28 sh:29 sw:2B

Instruções do tipo J. Valor do campo opcode em hexadecimal: j:2 jal:3.056101115162021252631

Formato R: op rs rt rd shamt funct

6 bits 5 bits 5 bits 5 bits 5 bits 6 bits

015162021252631

Formato I: op rs rt constante

6 bits 5 bits 5 bits 16 bits

0252631

Formato J: op endereço parcial

6 bits 26 bits

Número Nome Propósito

$0 $zero Sempre a zero$1 $at Registo para uso do assembler$2–$3 $v0–$v1 Valor retornado por sub-rotina$4–$7 $a0–$a3 Valores dos argumentos de uma sub-rotina$8–$15,$24,$25 $t0–$t9 Registos para valores temporários$16–$23 $s0–$s7 Registos preservados por sub-rotinas$26–$27 $k0–$k1 Reservados para sistema operativo (*)$28,$29,$30 $gp,$sp,$fp Reservados para funções especiais (*)$31 $ra Endereço de retorno da sub-rotina corrente

Linhas a sombreado indicam registos cujos valores devem ser preservados pelas sub-rotinas.(*) Registos não usados em AOCO.

Arquitetura e Organização de Computadores Pág. 53 de 100

Linguagem assembly — Exercícios resolvidos

6.2 Exercícios resolvidos

Exercício 1Para as seguintes expressões aritméticas (números inteiros de 32 bits), especifique ummapeamento de variáveis para registos e o fragmento de código assembly MIPS-32 que asimplementa.

f = g - (f + 5)a) f = A[12] + 17b)

O primeiro passo neste tipo de problemas é escolher uma atribuição de variáveis a registos. Cadavariável é atribuída a um registo. Como a arquitetura MIPS-32 dispõe de um número elevadode registos, trata-se geralmente de uma tarefa simples, porque se pode usar um registo diferentepara cada variável.

a) Uma possível atribuição de registos a variáveis é a seguinte:

f → $s0, g → $s1

O fragmento de código que realiza os cálculos desejados é:

addi $s0, $s0, 5 # Calcula f = f + 5sub $s0, $s1, $s0 # Calcula f = g - f